# 4. Serial ATA (SATA)

### 4.1 Das Interface aus funktioneller Sicht

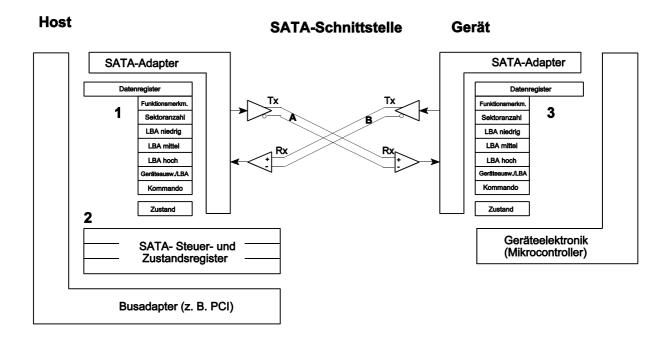

Serial ATA leistet im Grunde nicht mehr, als Daten zwischen zwei ATA-Registersätzen zu bewegen (Abb. 4.1 bis 4.4).

**Abb. 4.1** Serial ATA aus funktioneller Sicht. 1 - der ATA-Registersatz im Hostadapter; 2 - zusätzliche SATA-Steuer- und Zustandsregister; 3 - der ATA-Registersatz im Gerät

Die Anwendungssoftware sieht nach wie vor einen herkömmlichen ATA-Registersatz. Dieser befindet sich aber im Hostadapter und nicht im Gerät (Schattenregister). Die zusätzlichen Steuer- und Zustandsregister werden ausschließlich von der System- bzw. Gerätesteuersoftware verwendet. SATA bewegt die Registerinhalte bitseriell über zwei Leitungspaare A, B.

Typische Vorteile gegenüber anderen seriellen Hochgeschwindigkeits-Interfaces:

- geringere Kosten durch Beschränkung auf das vergleichsweise bescheidene Einsatzgebiet (kurze Leitungslängen, keine Multimaster-Konfigurationen, nur ein Gerät je Schnittstelle usw.),

- Abwärtskompatibilität,

- kein Overhead in der Anwendungssoftware. Besonders wichtig: der Kaltstart erfordert nicht mehr Software im ROM als bisher (demgegenüber hängt die Funktionsfähigkeit beispielsweise von USB oder Firewire von mehreren Software-Schichten ab; der Programmaufwand zur Unterstützung des Kaltstarts ist beträchtlich höher).

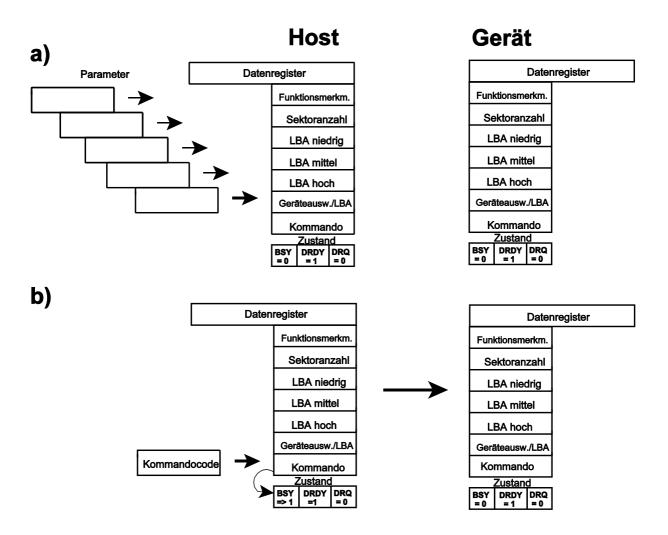

Abb. 4.2 Kommandoausführung (1): der Anfang. a) der Host trägt die Parameter in den Registersatz ein; b) die Parameterübergabe endet mit dem Eintragen des Kommandocodes. Daraufhin wird der Registersatz besetzt (BSY => 1), und sein Inhalt wird zum Gerät übertragen.

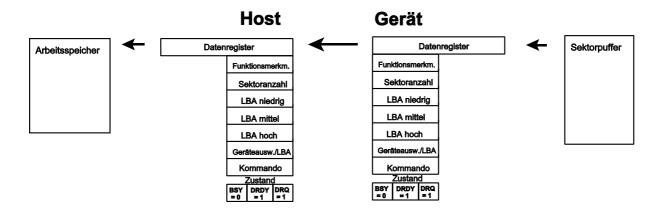

Abb. 4.3 Kommandoausführung (2): Datenübertragung (hier ein Leseablauf)

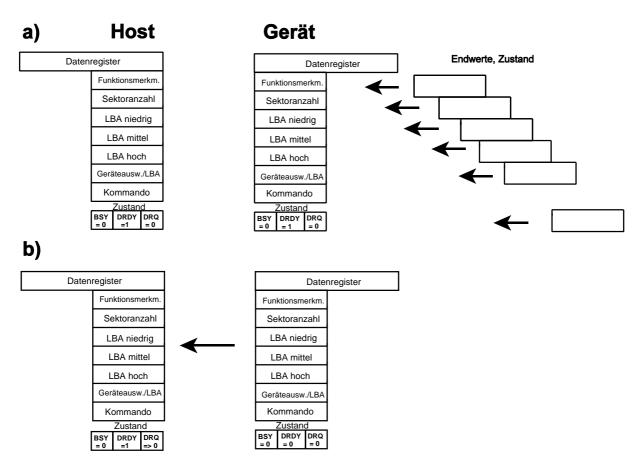

**Abb. 4.4** Kommandoausführung (3): das Ende. a) der Mikrocontroller des Gerätes trägt die Endwerte und den aktuellen Zustand in den Registersatz des Gerätes ein; b) der Inhalt des Registersatzes wird zum Host übertragen.

# 4.2 Signalkennwerte

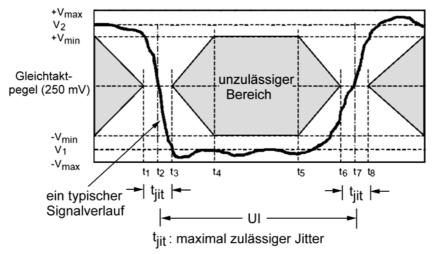

Serial ATA beruht auf der differentiellen Signalübertragung mit geringem Signalhub über Leitungspaare, die mit ihrem Wellenwiderstand abgeschlossen sind. Tabelle 4.1 enthält die wichtigsten Kennwerte. Abb. 4.5 zeigt das Augendiagramm der Schnittstelle.

| Kennwert                                                   | Nennwert               | Bereich                      |

|------------------------------------------------------------|------------------------|------------------------------|

| Einheitsintervall UI                                       | 666,667 ps             | 666,43670,12 ns              |

| Anstiegszeit t <sub>r</sub> , Abfallzeit t <sub>f</sub>    | 0,3 UI = 200 ps        | 0,20,41 UI = 133,33273,33 ps |

| Gleichtaktspannung V <sub>cm,dc</sub>                      | 250 mV                 | 200300 mV                    |

| Gegentaktspannung am Senderausgang $V_{\text{diff,tx}}$    | $500~\mathrm{mV_{PP}}$ | 400600 mV <sub>PP</sub>      |

| Gegentaktspannung am Empfängereingang $V_{\text{diff,rx}}$ | $400~\mathrm{mV_{PP}}$ | 325600 mV <sub>PP</sub>      |

| Ausgangsimpedanz (Sender), Eingangsimpedanz (Empfänger)    | 100 Ω                  | 85115Ω                       |

Tabelle 4.1 Kennwerte der SATA-Schnittstelle (1. Generation)

#### Hinweise:

1. Das Einheitsintervall entspricht einer Datenrate von 1,5 GBits/s und einer maximalen Impulsfolgefrequenz von 750 MHz (1 : 2 UI).

- 2. Eine Gegentaktspannung von 500 mV entspricht einem Signalhub von ± 250 mV gegen eine Bezugsspannung (Gleichtaktspannung) von + 250 mV.

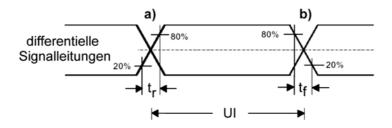

- 3. Anstiegs- und Abfallzeiten werden zwischen 20 und 80% des Signalhubs gemessen (Abb. 4.6).

Gegentaktspannung: V<sub>diff</sub> = V<sub>2</sub> - V<sub>1</sub>

Abb. 4.5 Das Augendiagramm

Abb. 4.6 Zeitkennwerte. a) Anstiegs-, b) Abfallzeit

## 4.3 Grundlagen der Signalübertragung

#### Codierungsverfahren

NRZ, 8B/10B. 8 Nutzbits werden in eine Folgen von 10 zu übertragenden Bits umgeschlüsselt. Nutzdatenrate (in Bits/s) deshalb = 0,8 • Datenrate (Bitrate) auf dem Interface.

### Verwendete Codezeichen:

- alle 256 Datenzeichen,

- die Steuerzeichen K28.3 und K28.5.

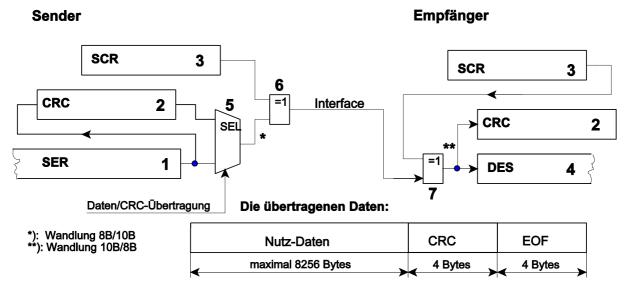

Fehlerkontrolle: mittels 32-Bit-CRC. Das CRC-Wort wird an die Nutzdaten angehängt (Abb. 4.7). Erkennungsvermögen: bis zu zwei 10-Bit-Bündelfehler in einem Datenstrom von 16384 Bytes Länge. Um die Wirksamkeit des CRC zu gewährleisten, ist die Länge des Datenstroms auf maximal 8256 Bytes beschänkt (erlaubt die Übertragung von 8 kBytes Nutzdaten). Der CRC betrifft die uncodierten Daten (8B).

### EMV-Vorkehrungen:

- 1. Scrambling/Descrambling: Wandlung des Datenstroms in ein pseudo-zufälliges Bitmuster (Abb. 4.7), um zu vermeiden, daß im Störspektrum übermäßige Spitzen auftreten.

- 2. Spread-Spektrum-Betrieb (kontinuierliches Verändern der Taktfrequenz in geringem Maße) ist zulässig (maximal 0,5% Frequenzverringerung (downspread)).

1 - Nutzdaten-Serialisierung; 2 - rückgekoppelte Schieberegister zur CRC-Bildung und - Kontrolle; 3 - rückgekoppelte Schieberegister für Scrambling und Descrambling; 5 - Sendedatenauswahl; 6, 7- XOR-Gatter.

Abb. 4.7 CRC-Kontrolle und Scrambling/Descrambling (Prinzipschaltbild)

Der gesamte Datenstrom (Nutzdaten + CRC) wird im Sender dem Scrambling unterworfen (XOR-Verknüpfung 6 mit dem Ausgang des rückgekoppelten Schieberegisters 3). Im Empfänger hebt die XOR-Verknüpfung 7 mit dem Ausgang des gleichartigen Schieberegisters 3 (liefert das gleiche Bitmuster) das Scrambling wieder auf (Descrambling).

#### Das Interface in Ruhe

Die Gegentaktspannung ist = 0, die Gleichtaktspannung beträgt 250 mV. Beide Leitungen eines Signalpaares führen somit + 250 mV.

### Sondersignalisierung (Out of Band Signaling OOB)

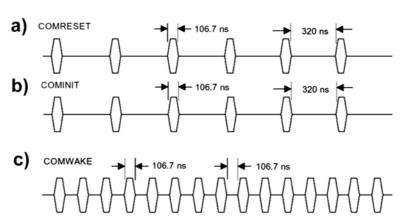

Die Sondersignalisierung dient dazu, ganz elementare Funktionen auszulösen. Hierzu werden bestimmte Signalfolgen auf das Interface gegeben, die einfach zu erzeugen und zu erkennen sind (Abb. 4.8).

Abb. 4.8 Sondersignalisierung (Out of Band Signaling OOB). Nähere Erklärung im folgenden Text

Die Sondersignaliserung beruht auf Bursts von je 160 Einheitsintervallen der Generation 1 (= 106,7 ns). In jedem Burst werden 4 sog. ALIGN-Primitives übertragen (das sind 32-Bit-Worte mit einer bestimmten festen Belegung). Die einzelnen Signalisierungen unterscheiden sich in der Dauer der Abstände zwischen den Bursts:

- a) COMRESET. Hierüber erzwingt der Host ein hartes Rücksetzen im Gerät. Abstand zwischen den Bursts: 320 ns. Mindestdauer der Signalisierung: 4 aufeinanderfolgende Bursts.

- b) COMINIT. Hierüber fordert das Gerät vom Host eine Initialisierung an. Abstand zwischen den Bursts: 320 ns (wie COMRESET, nur andere Richtung). Mindestdauer der Signalisierung: 4 aufeinanderfolgende Bursts.

- c) COMWAKE. Aufforderung zum Verlasssen von Stromsparzuständen. Kann sowohl vom Host als auch vom Gerät gesendet werden. Abstand zwischen den Bursts: 106,7 ns (gleiche Dauer wie Burst). Mindestdauer der Signalisierung: 6 aufeinanderfolgende Bursts.

### Kalibrierung

Der Wellenwiderstand der Signalwege ist mit  $100\,\Omega$  differentiell bzw. mit  $50\,\Omega$  (je Signalleitung) gegen Masse spezifiziert. Die Signalleitungen sind beidseitig abgeschlossen. Es ist vorgesehen, daß die Treiber ihre Ausgangsimpedanz an die tatsächliche Eingangsimpedanz des Empfängers anpassen. (Es handelt sich um ein Durchfahren des Wertebereiches, das dann beendet wird, wenn die Anpassung erreicht ist. Um dies zu erkennen, werden spezielle Prüfsignale über das Kabel übertragen.)

### Der Einschaltvorgang

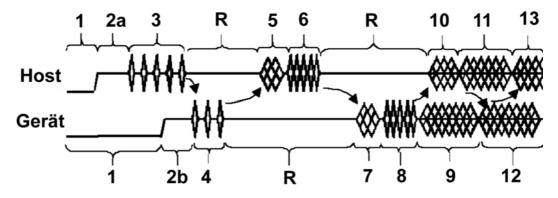

Abb. 4.9 veranschaulicht die Abläufe nach dem Einschalten von Host und Gerät.

**Abb. 4.9** Der Einschaltvorgang. R:Signalweg in Ruhe (+ 250 mV auf beiden Signalleitungen). Nähere Erklärung im folgenden Text

Der Ablauf des Einschaltvorgangs:

- 1) Host und Gerät ausgeschaltet. Interfacesignale werden über die Abschlußwiderstände auf Low-Pegel gehalten.

- 2) Speisespannung wird in Host (2a) und Gerät (2b) eingeschaltet. Interface gelangt in Ruhezustand (+ 250 mV auf allen Signalleitungen).

- 3) Host sendet COMRESET (für die Dauer des Einschaltrücksetzens),

- 4) das Gerät antwortet mit COMINIT,

- 5) Host gleicht den Leitungsabschluß seines Senders ab (Kalibrierung),

- 6) Host sendet COMWAKE,

- 7) Gerät gleicht den Leitungsabschluß seines Senders ab (Kalibrierung),

- 8) Gerät sendet COMWAKE (6 Bursts),

- 9) Gerät sendet ALIGN-Primitives,

- 10) Host sendet ALIGN-Zeichen D10.2.

- 11) Host sendet ALIGN-Primitives,

- 12) Gerät sendet SYNC-Primitives,

- 13) Host beginnt mit der normalen Arbeit.

Bis zu Punkt 8 erfolgen alle Übertragungen mit der Geschwindigkeit der 1. Generation (UI = 666,67 ps). Mit Punkt 9 versucht das Gerät, dem Host seine aktuelle Geschwindigkeit zu signalisieren. Antwortet der Host nicht innerhalb von 54,6 µs auf die angebotenen ALIGN-Primitives, so schaltet das Gerät die Geschwindigkeit zurück und versucht es noch einmal. Der Host sendet zunächst ALIGN-Zeichen D10.2 (Punkt 10) mit der geringsten Geschwindigkeit, die er unterstützt. Kann er die ALIGN-Primitives des Gerätes erkennen und die betreffende Geschwindigkeit unterstützen, so sendet er seinerseits ALIGN-Primitives mit der vom Gerät vorgegebenen Geschwindigkeit. Hat das Gerät diese ALIGN-Primitives erkannt, so sendet es (als Bestätigung) SYNC-Primitives zum Host, und die normale Arbeit kann beginnen.

Kann der Host innherhalb von 880 µs keine ALIGN-Primitives des Gerätes erkennen, so wiederholt er die gesamte Einschaltfolge von Punkt 3 an ("ewige" Wiederholung, die ggf. von übergeordneter Software beendet wird).

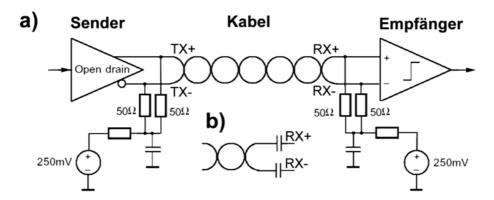

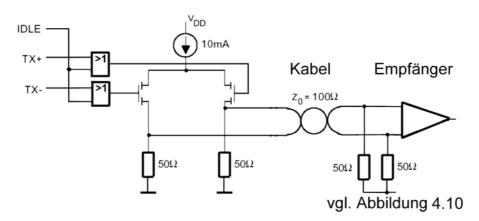

## 4.4 Der Signalweg

Abb. 4.10 zeigt den Aufbau eines SATA-Signalweges; Abb. 4.11 veranschaulicht das Prinzip einer Treiberstufe.

**Abb. 4.10** Der SATA-Signalweg. a) gleichspannungsgekoppelter Signalweg; b) Wechselspannungskopplung (wahlweise)

Die Spitzfindigkeiten der 8B/10B-Codierung dienen u. a. dazu, eine (näherungsweise) gleichstromfreie Übertragung zu ermöglichen. Deshalb kann man den Empfänger auch über Kondensatoren ankoppeln. Leitungsabschluß: mit jeweils 50  $\Omega$  je Signalleitung. Die Spannungsquellen (250 mV) halten die Signalleitungen im Ruhezustand auf dem geforderten Pegel.

Abb. 4.11 Signalweg mit Treiberstufe (Prinzipschaltung)

Der Treiber ist hier mit zwei Open-Drain-Stufen aufgebaut. Wird ein Transistor angesteuert, so fließen die 10 mA der Stromquelle über den jeweiligen Abschlußwiderstand und rufen dort einen Spannungsbfall von ca. 500 mV hervor. Bei Ansteuerung über TX+ oder Tx+ wird nur jeweils einer der Transistoren aktiviert, so daß an der betreffenden Leitung 500 mV anliegen, während die jeweils andere Leitung über ihren Abschlußwiderstand auf Massepotential gehalten wird. Ist IDLE aktiv, so werden beide Transistoren angesteuert, und die 10 mA fließen über die Paralleleschaltung der beiden Abschlußwiderstände. Das ergibt den geforderten Pegel von 250 mV (Ruhezustand).

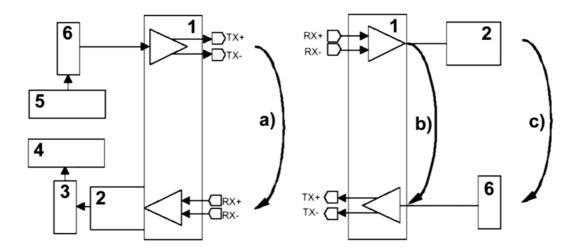

# 4.5 Prüfvorkehrungen

Der Standard sieht mehrere Testmuster zum Prüfen des Interfaces vor. Des weiteren können Senderausgänge auf Empfängereingänge zurückgeführt werden (Kurzschlußprüfung (Loopback Testing); Abb. 4.12).

Abb. 4.12 Konfigurationen der Kurzschlußprüfung (Loopback Testing). 1 - Interfacekoppelstufen; 2 - Datenrückgewinnung; 3 - Deserializer; 4 - Testmustererkennung; 5 - Testmustererzeugung; 6 - Serializer. Nähere Erklärung im folgenden Text

Abb. 4.12 veranschaulicht folgende Prüfschleifen:

- a) lokale analoge Prüfschleife (Near-End Analog Loopback). Herstellerspezifisch (wahlfrei).

- b) analoge Fernprüfschleife (Far-End Analog Loopback). Herstellerspezifisch (wahlfrei).

- c) digitale Fernprüfschleife (Far-End Digital Loopback). Schließt Taktsynchronisation im Empfänger ein (Retiming). Vom Standard gefordert (obligatorisch).

Es kann in beiden Richtungen geprüft werden (vom Host zum Gerät und umgekehrt). Einstellung der Prüfschleifen: über spezielle Informationsformate (BIST Activate Frames).

### 4.6 Informationsstrukturen

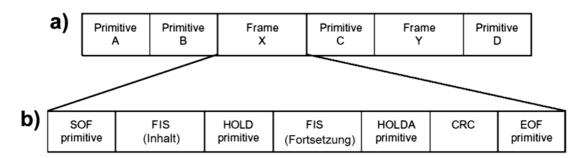

Es gibt zwei elementare Informationstrukturen: Primitives und Frames (Abb. 4.13). Alle Strukturen beruhen auf dem 32-Bit-Wort (DWord) als kürzester Einheit. Infolge der 8B/10B-Codierung werden je Dword 40 Bits übertragen.

Primitives sind Steuerstrukturen, die jeweils 1 Dword lang sind und eine feste Codierung haben. Alle Primitives beginnen mit einem Steuerzeichen des 8B/10B-Codes.

Frames sind Strukturen, die Nutzdaten enthalten. Sie bestehen aus Primitives, dem eigentlichen Inhalt und einem CRC-DWord. Der eigentliche Inhalt ist in Form sog. Frame Information Structures (FIS's) organisiert.

a) aus Primitives und Frames bestehender Informationsfluß; b) Aufbau eines Frames. SOF = Start of Frame; FIS = Frame Information Structure (der eigentliche Inhalt), CRC = Fehlerkontrollcode; EOF = End of Frame. Es ist weiterhin angedeutet, wie der Ablauf zeitweilig angehalten werden kann: HOLD = Sender kann zeitweilig keine Daten liefern; HOLDA (Hold Acknowledge) = Bestätigung einer HOLD-Signalisierung der jeweils anderen Einrichtung.

#### Abb. 4.13 Elementare Informationsstrukturen

Die folgenden Abb. 4.14 bis 4.21 zeigen die einzelnen FIS-Formate. Da es sich nur um einen Überblick handelt, verzichten wir auf die Erklärung der einzelnen Steuerbits.

#### Hinweis:

Ein "erw." am Schluß der Registerbezeichnungen kennzeichnet das zweite (im jeweils vorhergehenden Schreibzugriff geladene) Register der 48-Bit-Adressierung (vgl. Kapitel 2).

| 0 | Funktionsmerkmale    | Kommando      | C R R res. (= 0)  | FIS-Typ (27H)    |  |  |

|---|----------------------|---------------|-------------------|------------------|--|--|

| 1 | Geräteauswahl        | LBA hoch      | LBA mittel        | LBA niedrig      |  |  |

| 2 | Funktionsm. erw.     | LBA hoch erw. | LBA mittel erw.   | LBA niedrig erw. |  |  |

| 3 | Gerätesteuerregister | res. (= 0)    | Sektoranzahl erw. | Sektoranzahl     |  |  |

| 4 | res. (= 0)           | res. (= 0)    | res. (= 0)        | res. (= 0)       |  |  |

Abb. 4.14 FIS für Registertransport vom Host zum Gerät

| 0 | Fehlerregister | Zustandsregister | R I R res. (= 0)  | FIS-Typ (34H)    |  |  |  |

|---|----------------|------------------|-------------------|------------------|--|--|--|

| 1 | Geräteauswahl  | LBA hoch         | LBA mittel        | LBA niedrig      |  |  |  |

| 2 | res. (= 0)     | LBA hoch erw.    | LBA mittel erw.   | LBA niedrig erw. |  |  |  |

| 3 | res. (= 0)     | res. (= 0)       | Sektoranzahl erw. | Sektoranzahl     |  |  |  |

| 4 | res. (= 0)     | res. (= 0)       | res. (= 0)        | res. (= 0)       |  |  |  |

Abb. 4.15 FIS für Registertransport vom Gerät zum Host

| 0 | Fehlerregister | Zustandsregister | R | I | R | res. (= 0) | FIS-Typ (A1H) |  |  |  |  |

|---|----------------|------------------|---|---|---|------------|---------------|--|--|--|--|

| 1 |                | res. (= 0)       |   |   |   |            |               |  |  |  |  |

Abb. 4.16 FIS für Bittransport vom Gerät zum Host. Hiermit werden die Bits übertragen, die nur vom Gerät geschrieben werden können. BSY und DRQ werden im Host nicht geändert

| 0 | res. (= 0) | res. (= 0) | res. (= 0) | FIS-Typ (39H) |

|---|------------|------------|------------|---------------|

| _ | ( - /      | ( - /      | ( - )      | ) [- ()       |

Abb. 4.17 FIS für DMA-Aktivierung (vom Gerät zum Host)

| 0 | res. (= 0)                   | res. (= 0) R I D res. (= 0) FIS-Typ (41H) |  |  |  |  |  |  |  |  |

|---|------------------------------|-------------------------------------------|--|--|--|--|--|--|--|--|

| 1 | Pufferidentifizierer niedrig |                                           |  |  |  |  |  |  |  |  |

| 2 | Pufferidentifizierer hoch    |                                           |  |  |  |  |  |  |  |  |

| 3 | res. (= 0)                   |                                           |  |  |  |  |  |  |  |  |

| 4 | Puffer-Offset                |                                           |  |  |  |  |  |  |  |  |

| 5 | Byteanzahl                   |                                           |  |  |  |  |  |  |  |  |

| 6 | res. (= 0)                   |                                           |  |  |  |  |  |  |  |  |

**Abb. 4.18** FIS zum Vorbereiten eines DMA-Zugriffs (DMA Setup). Betrifft beide Übertragungsrichtungen

| 0 | Funktionsmerkmale | Zustandsregister | R                              | Ι | D  | res. (= 0)  | FIS-Typ (5FH)    |  |  |

|---|-------------------|------------------|--------------------------------|---|----|-------------|------------------|--|--|

| 1 | Geräteauswahl     | LBA hoch         |                                |   | LE | BA mittel   | LBA niedrig      |  |  |

| 2 | res. (= 0)        | LBA hoch erw.    |                                | L | ВА | mittel erw. | LBA niedrig erw. |  |  |

| 3 | neuer Zustand     | res. (= 0)       | Sektoranzahl erw. Sektoranzahl |   |    |             |                  |  |  |

| 4 | res.              | (= 0)            | Byteanzahl                     |   |    |             |                  |  |  |

Abb. 4.19 FIS zum Vorbereiten eines PIO-Zugriffs (PIO Setup). Vom Gerät zum Host

| 0 | res. (= 0)    | res. (= 0) | res. (= 0) | FIS-Typ (46H) |  |  |  |  |  |  |

|---|---------------|------------|------------|---------------|--|--|--|--|--|--|

| 1 | 1. DWord      |            |            |               |  |  |  |  |  |  |

| 2 | 2. Dword      |            |            |               |  |  |  |  |  |  |

|   |               |            |            |               |  |  |  |  |  |  |

| n | letztes DWord |            |            |               |  |  |  |  |  |  |

**Abb. 4.20** FIS zur Datenübertragung (1...2048 Dwords = 4...8192 Bytes). Beide Übertragungsrichtungen

| 0 | res. (= 0) | ТА        | S L | F | P R | ٧ | res. (= 0) | FIS-Typ (58H) |  |  |

|---|------------|-----------|-----|---|-----|---|------------|---------------|--|--|

| 1 |            | Prüfdaten |     |   |     |   |            |               |  |  |

| 2 |            | Prüfdaten |     |   |     |   |            |               |  |  |

**Abb. 4.21** FIS zum Auslösen von Prüfvorgängen (BIST Activate). Die Bits T, A, S usw. dienen zur Prüfablaufsteuerung und zum Schalten der Prüfschleifen (vgl. Abb. 4.12)

# 4.7 Die SATA-Steuer- und Zustandsregister

Die SATA-Spezifikation sieht im Host bis zu 16 Register zu 32 Bits vor (Serial ATA Status and Control Registers; SCRs). Zur Emulation der herkömmlichen ATA-Programmschnittstelle sind sie nicht erforderlich. Es werden zunächst die ersten 3 Register belegt (Abb. 4.22, Tabellen 4.2 und 4.3):

- SCR0: Zustandsregister (SStatus). Beschreibt den aktuellen Zustand von Gerät und Hostadapter. Nur Lesen.

- SCR1: Fehlerregister (SError). Enthält genauere Fehlerangaben. Lesen und selektives Löschen (Schreibzugriffe löschen einzelne Bits (Schreiben einer 1 löscht das Bit in der betreffenden Position, Schreiben einer 0 läßt es unverändert)).

- SCR2: Steuerregister (SControl). Ermöglicht es, Einzelheiten der Schnittstellensteuerung zu beeinflussen. Lesen und Schreiben.

| 0 |                                             | res. (= 0) |  |  |  |  |  |  |    | IPM |   |   |    | SPD |   |   |    | DET |   |  |

|---|---------------------------------------------|------------|--|--|--|--|--|--|----|-----|---|---|----|-----|---|---|----|-----|---|--|

| 1 | res. (= 0) E P C T res. (= 0) M I res. (= 0 |            |  |  |  |  |  |  | )) | F   | Т | S | Η  | С   | D | В | W  | I   | N |  |

| 2 |                                             | res. (= 0) |  |  |  |  |  |  |    | М   |   |   | SF | PD  |   |   | DE | ΞT  |   |  |

Abb. 4.22 SATA-Steuer- und Zustandsregister

| DET: Geräteerkennung und l                                                                                                                                                                                          | Betriebszustand des Interfaces                                                                                                                                                                                                                                |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| <ol> <li>kein Gerät erkannt,</li> <li>Gerät erkannt, aber keine Kommunikation<br/>aufgebaut,</li> <li>Gerät erkannt und Kommunikation aufgebaut,</li> <li>Interface außer Betrieb oder Kurzschlußprüfung</li> </ol> | nichts tun (keine Geräteerkennung oder Initialisierung),     Kommunikation aufbauen (hartes Rücksetzen),     Interface stillsetzen                                                                                                                            |  |  |  |  |

| SPD: Geschwindigkeitser                                                                                                                                                                                             | rkennung und -steuerung                                                                                                                                                                                                                                       |  |  |  |  |

| <ul><li>0: kein Gerät erkannt oder Kommunikation nicht aufgebaut,</li><li>1: Geschwindigkeit gemäß Generation 1 vereinbart</li></ul>                                                                                | keine Einschränkung bei Vereinbarung der Geschwindigkeit,     nur Geschwindigkeit der Generation 1 vereinbaren                                                                                                                                                |  |  |  |  |

| IPM: Stroms                                                                                                                                                                                                         | parsteuerung                                                                                                                                                                                                                                                  |  |  |  |  |

| <ol> <li>kein Gerät erkannt,</li> <li>Interface aktiv,</li> <li>Stromsparzustand PARTIAL,</li> <li>Stromsparzustand SLUMBER.</li> </ol>                                                                             | <ol> <li>keine Einschränkungen des Stromsparbetriebs,</li> <li>Übergang in Stromsparzustand PARTIAL wird verhindert,</li> <li>Übergang in Stromsparzustand SLUMBERwird verhindert,</li> <li>Übergänge in beide Stromsparzustände werden verhindert</li> </ol> |  |  |  |  |

**Tabelle 4.2** SCR-Registerbelegungen (1). Links SCR0 (Zustandsanzeige), rechts SCR2 (Zustandseinstellung)

| ERR-Feld (Bits 3116)                             | DIAG-Feld (Bits 150)                                |

|--------------------------------------------------|-----------------------------------------------------|

| E: interer Fehler im Hostadapter,                | F: nicht erkannter FIS-Typ,                         |

| P: Protokollfehler (z. B. Empfang ungültiger     | T: fehlerhafter Zustandsübergang                    |

| Frames),                                         | (Transportschicht),                                 |

| C: Fehlerbehebungsversuch erfolglos; bleibender  | S: fehlerhafter Zustandsübergang                    |

| Fehler,                                          | (Verbindungsschicht),                               |

| T: transienter Datenintegritätsfehler. Noch kein | H: Handshaking-Fehler,                              |

| Fehlerbehebungsversuch.                          | C: CRC-Fehler,                                      |

| M: behobener Kommunikationsfehler,               | D: Disparity-Fehler (8B/10B-Übertragung),           |

| Kommunikation wurde wieder aufgebaut.            | B: 10B/8B-Decodierfehler,                           |

| I: behobener Datenintegritätsfeher (erfolgreiche | W: COMWAKE-Signalisierung erkannt,                  |

| Wiederholung)                                    | I: interner Fehler in der physischen Schnittstelle, |

|                                                  | N: Änderung im Bereitschaftszustand der             |

|                                                  | physischen Schnittstelle                            |

## 4.8 Steckverbinder und Kabel

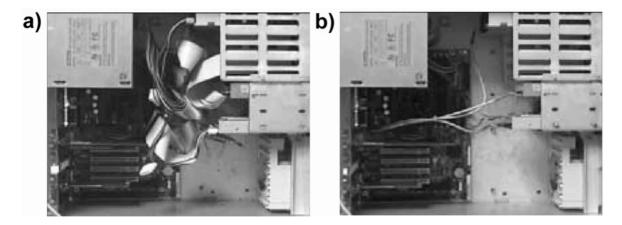

Die Verkabelung ist ein offensichtlicher Vorteil dieses Interfaces (Abb. 4.23). Die Abb. 4.24 bis 4.29 geben einen Überblick über Steckverbinder und Kabel.

**Abb. 4.23** Geräteverkabelung im Vergleich (Intel). a) die herkömmliche (parallele) ATA-Schnittstelle, b) Serial ATA

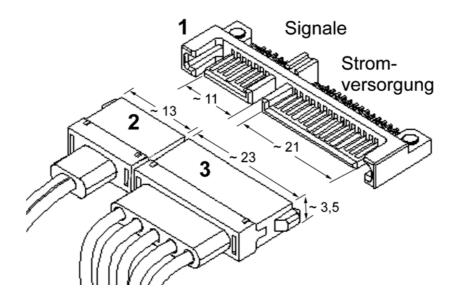

**Abb. 4.24** Steckverbinder und Kabel. 1 - SATA-Stromversorgungsanschluß; 2 - SATA-Interfaceanschluß; 3 - herkömmlicher Stromversorgungsanschluß; 4 - SATA-Interfacekabel

**Abb. 4.25** Die Steckverbinder am Gerät. 1 - Kombinationssteckverbinder (Signale + Stromversorgung) am Gerät; 2 - Kabel mit Signalstecker; 3 - Kabel mit Stromversorgungsstecker.

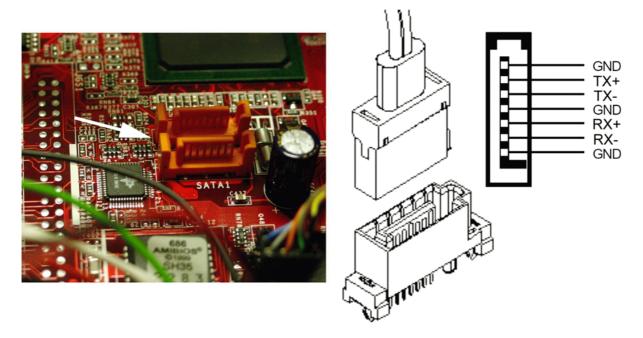

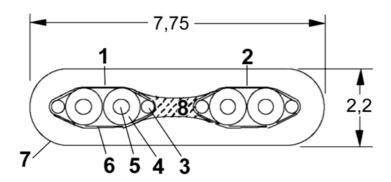

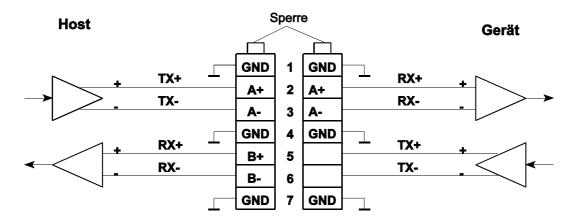

Abb. 4.26 Der hostseitige Signalsteckverbinder. Rechts außen die Anschlußbelegung

Der Signalsteckverbinder hat 7 Kontakte, der Stromversorgungssteckverbinder 15. Alle Kontakte befinden sich jeweils in einer Reihe: Kontaktabstand: 1,27 mm (0,05"). Die Signalsteckverbinder von Gerät und Host sind gleichartig. Zur Kontaktbelegung siehe Tabelle 4.4.

- 1, 2 die beiden Signalleitungspaare; 3 zusätzliche Masseleitung (28 AWG); 4 Isolation,

- 5 Leiter (26 AWG); 6- umhüllende Abschirmung (aluminiumbeschichtete Polyesterfolie);

- 7 Außenhülle (PVC); 8 Hohlraum. Leiterwerkstoff: Cu-Volldraht, verzinnt.

### Abb. 4.27 Ein Signalkabel im Querschnitt

Die Signaladern in einem Paar liegen parallel nebeneinader (keine Verdrillung). Wellenwiderstand (differentiell): 100 Ohm, Kapazität: 42 pF/m, Signallaufzeit: 4,25 ns/m. Die Kabel dürfen auch anders aufgebaut sein (z. B. als Rundkabel mit verdrillten Leitungspaaren), sofern sie die elektrischen Kennwerte einhalten.

TX: Sendedaten RX: Empfangsdaten

Abb. 4.28 Zur Belegung des Signalkabels

Es handelt sich um eine durchgehende Punkt-zu-Punkt-Verbindung mit einem abgeschirmten Leitungspaar je Übertragungsrichtung (differentielle Signalübertragung) und zusätzlichen Masseverbindungen. Dabei ist es gleichgültig, ob Gerät und Host über Kabel verbunden oder direkt zusammengesteckt werden (z. B. über eine Backplane).

### Speisespannungen

Gemäß Standard sind folgende Speisespamnnungen vorgesehen. + 3,3 V, + 5 V und + 12 V (Tabelle 4.5). Es hängt vom jeweils angeschlossenen Gerät ab, welche Speisespannungen benötigt werden. Deshalb ist es zulässig, einzelne Speisespannungen wegzulassen. Wird aber eine Speisespannung zugeführt, so muß sie an allen betreffenden Kontakten (es sind jeweils drei) anliegen.

| Bezeichnung | Belegung    | Anmerkungen                                                     |

|-------------|-------------|-----------------------------------------------------------------|

| S1          | Masse (GND) | Kontaktvoreilung: 1                                             |

| S2          | A+          | Signalpaar vom Host zum Gerät (Host: TX+, TX-; Gerät: RX+, RX-) |

| S3          | A-          |                                                                 |

| S4          | Masse (GND) | Kontaktvoreilung: 1                                             |

| S5          | B+          | Signalpaar vom Gerät zum Host (Host: RX+, RX-; Gerät: TX+, TX-) |

| S6          | B-          |                                                                 |

| S7          | Masse (GND) | Kontaktvoreilung: 1                                             |

Tabelle 4.4 Kontaktbelegung des Signalsteckverbinders

| Bezeichnung | Belegung    | Anmerkungen                  |

|-------------|-------------|------------------------------|

| P1          | $V_{33}$    |                              |

| P2          | $V_{33}$    | + 3,3 V                      |

| Р3          | $V_{33}$    | + 3,3 V; Kontaktvoreilung: 1 |

| P4          | Masse (GND) | Kontaktvoreilung: 2          |

| P5          | Masse (GND) | Kontaktvoreilung: 1          |

| Р6          | Masse (GND) | Kontaktvoreilung: 1          |

| P7          | $V_5$       | + 5 V; Kontaktvoreilung: 1   |

| P8          | $V_5$       | + 5 V                        |

| Р9          | $V_5$       |                              |

| P10         | Masse (GND) | Kontaktvoreilung: 1          |

| P11         | reserviert  |                              |

| P12         | Masse (GND) | Kontaktvoreilung: 2          |

| P13         | $V_{12}$    | + 12 V; Kontaktvoreilung: 1  |

| P14         | $V_{12}$    | + 12 V                       |

| P15         | $V_{12}$    |                              |

Tabelle 4.5 Kontaktbelegung des Stromversorgungssteckverbinders

### Kontaktvoreilung:

Sie ist nur beim kabellosen Stecken (über Kombinationssteckverbinder auf beiden Seiten) von Bedeutung. Die Steckreihenfolge:

- Masse über P4 und P12 (Kontaktvoreilung 2),

alle weiteren Massekontakte sowie die Speisespannungskontakte P3, P7, P13 (Kontaktvoreilung 1),

- 3. alle anderen Kontakte (keine Voreilung).

Kontaktbelastbarkeit: wenigstens 1,5 A je Kontakt.