# 1. Grundlagen

# 1.1 Einführung

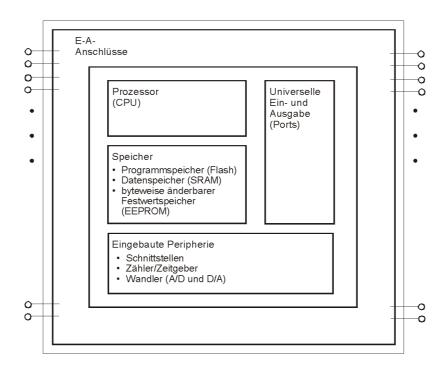

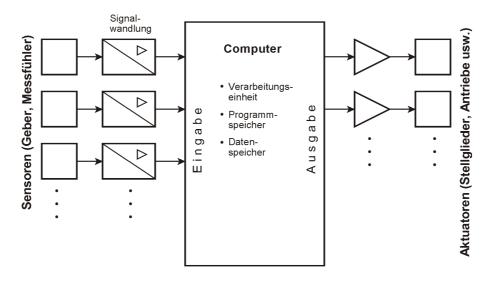

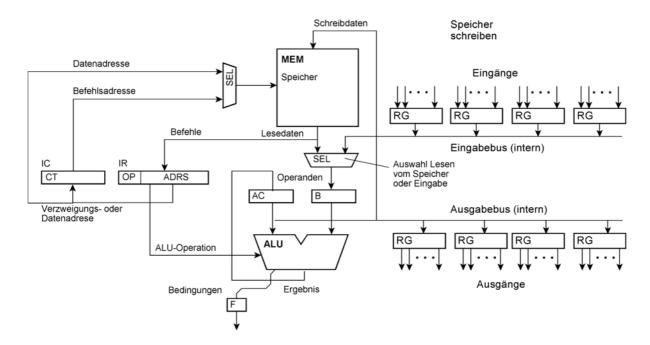

Die weitaus meisten Anwendungsaufgaben der Steuerungs-, Regelungs- und Automatisierungstechnik werden heutzutage mit Mikrocontrollern gelöst. Der Mikrocontroller ist ein vollständiger Computer in einem einzigen Schaltkreis. Programmspeicher, Datenspeicher und die Funktionseinheiten der Ein- und Ausgabe sind eingebaut. Somit stehen alle E-A-Anschlüsse zum Lösen der Anwendungsaufgabe zur Verfügung (Abbildung 1.1). Die einfachsten Systeme enthalten einen einzigen Mikrocontroller, dessen Anschlüsse direkt mit der jeweiligen Anwendungsumgebung verbunden sind, also mit Sensoren, Leistungsstufen, Bedienelementen, Anzeigeeinrichtungen usw. (Abbildung 1.2). Die Anwendungsfunktionen werden vom Programm erbracht, das im Mikrocontroller läuft. Es fragt alle Eingangsbelegungen ab und stellt alle Ausgangsbelegungen ein.

**Abb. 1.1** Ein Mikrocontroller. Alle Funktionseinheiten befinden sich im selben Schaltkreis.

# Zur Entwicklungsgeschichte

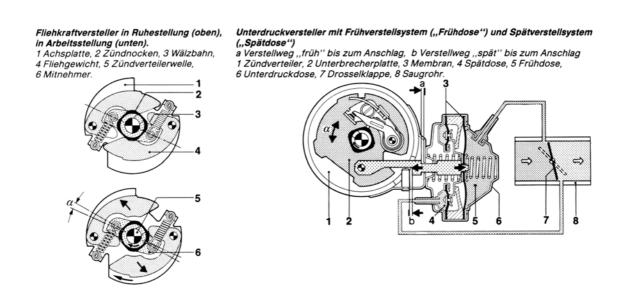

Als es noch gar keine Computer gab, blieb den Erfindern und Entwicklern kaum etwas anderes übrig, als nach geeigneten physikalischen Effekten und technischen Wirkprinzipien zu suchen und diese Ansätze bis hin zum brauchbaren Gerät konstruktiv durchzubilden. Hierbei sind nicht selten wirklich geniale Lösungen geschaffen worden. Ein typisches Beispiel ist der Zündverteiler im Auto. Die Aufgabe der Informationsverarbeitung besteht darin, den Zündzeitpunkt in Abhängigkeit von den aktuellen Betriebsverhältnissen des Motors zu bestimmen. Herkömmlicherweise hat man zwei Betriebskennwerte berücksichtigt: die Drehzahl (über Fliehgewichte – Fliehkraftverstellung) und die Belastung (über den Unterdruck im Saugrohr – Unterdruckverstellung). Abbildung 1.3 veranschaulicht, dass es sich um wirklich trickreiche mechanische Lösungen handelt.

Abb. 1.2 Heuzutage steht der Mikrocontroller im Mittelpunkt.

**Abb. 1.3** Informationsverarbeitung "auf mechanisch" – der herkömmliche Zündverteiler (Bosch) $^1$ .

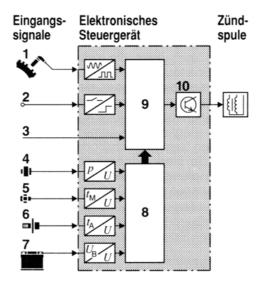

Der Mikrocontroller ermöglicht es, das Erfassen der eingangsseitigen Kenngrößen und das Auslösen der ausgangsseitigen Wirkungen von der Informationsverarbeitung zu trennen (Abbildung 1.4). Die meisten Einsatzfälle lassen sich in einem allgemeinen Blockschaltbild ähnlich Abbildung 1.2 darstellen.

<sup>1:</sup> Welchem Windows- oder gar Linux-Programmierer würde wohl sowas einfallen?

**Abb. 1.4** Informationsverarbeitung mit Mikrocontroller – die elektronische Zündung (Bosch).1 - Motordrehzahl\*; 2 - Schaltersignale; 3 - CAN-Bus (zur Vernetzung mit anderen Einrichtungen im Fahrzeug); 4 - Saugrohrdruck\*); 5 - Motortemperatur\*); 6 - Ansauglufttemperatur\*); 7 - Batteriespannung; 8 - Mikrocomputer; 9 - Analog-Digital-Wandler; 10 - Leistungsstufe. \*): Sensoren.

Wer heutzutage eine solche Aufgabe zu lösen hat, muss sich nach passenden Gebern und Messfühlern (Sensoren) und Stellgliedern oder Antrieben (Aktuatoren) umsehen sowie einen geeigneten Computer heraussuchen. (Offensichtlich bereitet das – zumindest in den weitaus meisten Fällen – beträchtlich weniger Mühe, als sich eine Anordnung ähnlich Abbildung 1.3 auszudenken.) Die Hauptarbeit besteht (meistens) nicht in der konstruktiven Durchbildung, sondern im Programmieren – es sind brauchbare Algorithmen zu (er)finden und in zuverlässig funktionierende Programme umzusetzen. Die Informationsverarbeitung gemäß dem Schema von Abbildung 1.2 hat sich weithin durchgesetzt – und zwar auch für Aufgaben, die man bisher schon vergleichsweise kostengünstig mit mechanischen oder elektromechanischen Mitteln lösen konnte.

In den 70er Jahren des vorigen Jahrhunderts wurde es möglich, Schaltkreise mit mehreren tausend Transistoren zu fertigen. Damals schon hätte man die meisten Anwendungsschaltungen auf einem einzigen Schaltkreis unterbringen können. Die Schaltkreisfertigung ist aber nur dann wirtschaftlich, wenn es sehr große Stückzahlen sind. Auch ist es sehr aufwendig, solche Schaltkreise zu entwickeln. In Gegensatz zur herkömmlichen Leiterplattentwicklung kann man nicht einfach probieren und Entwurfsfehler mit Draht beseitigen. Deshalb ist man darauf gekommen, universelle Schaltkreise zu schaffen, die in hohen Stückzahlen abgesetzt werden können. Nun gibt es nichts Vielseitigeres als den Universalrechner. Auf Grundlage einer überschaubaren, wohlbekannten Schaltungsstruktur kann man alles implementieren, was den Charakter eines Algorithmus hat - und das sind alle anwendungspraktisch in Betracht kommenden Abläufe und Informationswandlungen. Die Grenzen ergeben sich lediglich aus der Speicherkapazität und der Programmlaufzeit. Man baue einen kleinen Computer, versehe ihn mit universellen Anschlußschaltungen – und die Bauelementefrage ist grundsätzlich gelöst. An die Stelle der anwendungsspezifischen Schaltungsentwicklung tritt das Programmieren. Programme kann man noch viel leichter ändern als Leiterplatten. Hat man die Grundfertigkeiten des Programmierens erst einmal verinnerlicht, kann man sich der Lösung vieler Probleme durch fortlaufendes Probieren – mit anderen Worten, durch unbekümmertes Hacken – nach und nach annähern.

Die meisten Mikrocontroller werden nicht deswegen eingesetzt, weil es etwas zu rechnen gibt, sondern nur, um bestimmte Funktionen billiger zu erledigen als dies mit zweckgebundenen Schaltungen möglich wäre. In solchen Fällen kommt es oftmals auf geringste Hardwarekosten an. Der Schaltkreis ist soweit wie irgend möglich auszunutzen. Des zwingt oftmals zur maschinennahen Programmierung, zur Nutzung ungewöhnlicher Programmiertechniken – und nicht selten zum Tricksen auf Biegen und Brechen.

Bereits in den siebziger Jahren des vorigen Jahrhunderts waren in vielen Anwendungsfällen Mikrocontroller kostengünstiger als herkömmliche mechanische Lösungen<sup>2</sup>. Überall dort, wo Tasten und Schalter auszuwerten, Anzeigen anzusteuern und Schaltvorgänge auszulösen sind, war schon damals der Mikrocontroller das Mittel der Wahl.

Um derartige Anwendungslösungen auszuarbeiten, sind folgende grundsätzliche Aufgaben zu lösen:

- Es ist zunächst einmal zu erkennen, ob diese Einfachlösung ausreicht oder nicht.

- Ein passender Mikrocontroller ist auszuwählen.

- Dessen Ausstattung ist zweckmäßig auszunutzen.

- Er ist vernünftig zu programmieren. Hierzu sind geeignete Programmiermodelle und Programmierwerkzeuge auszuwählen.

- Es ist alles zum Laufen zu bringen.

Aus der Vielfalt der Problemstellungen – und dem üblichen Termindruck – ergeben sich typische Arbeitsbedingungen:

- Die komplette Anwendungslösung ist von Grund auf auszuarbeiten.

- Es gibt ein beträchtliches Maß an Wahlfreiheit (System- und Prozessorarchitekturen, Schaltkreise, Programmiermodelle usw.).

- Die Ressourcen sind knapp.

- Die Problemlösung steht unter Zeit- und Kostendruck es muss alles schnell gehen und darf nichts kosten.

- Bei den Materialkosten kommt es oft auf die Stellen nach dem Komma an.

- Wir haben weder genügend Zeit noch können wir, um Schwierigkeiten aus dem Wege zu gehen, auf immer dickere Prozessoren oder Systeme zurückgreifen.

- Man kann nicht alles haben.

- Es läuft keineswegs alles ideal man muss sich halt zu helfen wissen ...

Die typische Entwicklungsaufgabe ist eine Allround-Aufgabe (Abbildung 1.5):

- Die grundsätzliche Systemlösung ist zu finden.

- Die Bauelemente sind auszuwählen.

- Die Hardware ist zu entwerfen und zwar unter Berücksichtigung aller Anforderungen der Praxis (EMV, ESD, Prüfbarkeit, wirtschaftliche Fertigung, Service (fertigungs-, prüf- und servicegerechter Entwurf)).

- Die Software ist zu erstellen.

<sup>2:</sup> Und zwar auch für Probleme, die gar nicht besonders kompliziert sind. Eine der ersten Anwendungen am Massenmarkt war die Steuerung einfacher Mikrowellengeräte. Hier hatte der Mikrocontroller nur die Funktion einer Zeitschaltuhr zu übernehmen.

- Falls erforderlich, ist eine Testumgebung aufzubauen.

- Es ist alles zum Laufen zu bringen.

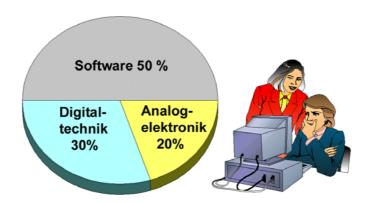

**Abb. 1.5** Richtwerte. Das typische Entwicklungsvorhaben ist von ein bis zwei Ingenieuren in nicht mehr als sechs Monaten zu bewältigen. 50 % der Entwicklungsaufwendungen betreffen die Software, 30 % die Digitaltechnik und 20 % die analogen Schaltungen (nach Hewlett-Packard).

# 1.2 Elementare Programmabläufe und Programmbeispiele

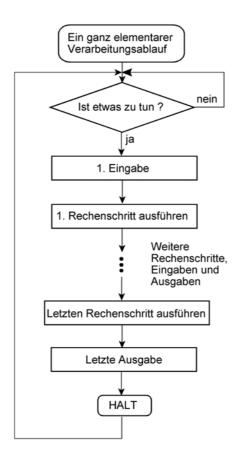

Typische Anwendungsaufgaben führen auf grundsätzliche Programmschleifen, die folgende Schritte enthalten (Abbildung 1.6):

- 1. Eingabe. Die Eingänge lesen (Sensoren, Bedienfelder usw.).

- 2. Verarbeitung. Die eigentlichen Verarbeitungs- und Steuerabläufe ausführen. Hierbei werden der Folgezustand und die Ausgangsdaten bestimmt.

- 3. Ausgabe. Die Ausgänge schreiben (Anzeigen, Leistungsstufen usw.).

- 4. Zurück zu Schritt 1. Beim nächsten Durchlauf arbeitet die Schleife mit dem Folgezustand, der in Schritt 2 ermittelt wurde.

Abb. 1.6 Die typische Programmschleife einer Anwendungslösung.

Das Prinzip soll zunächst anhand überschaubarer Anwendungen veranschaulicht werden.

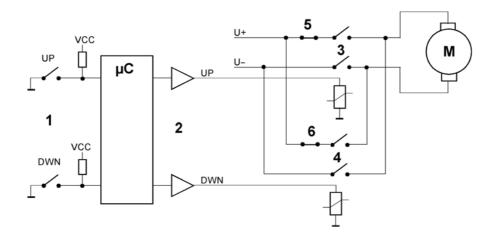

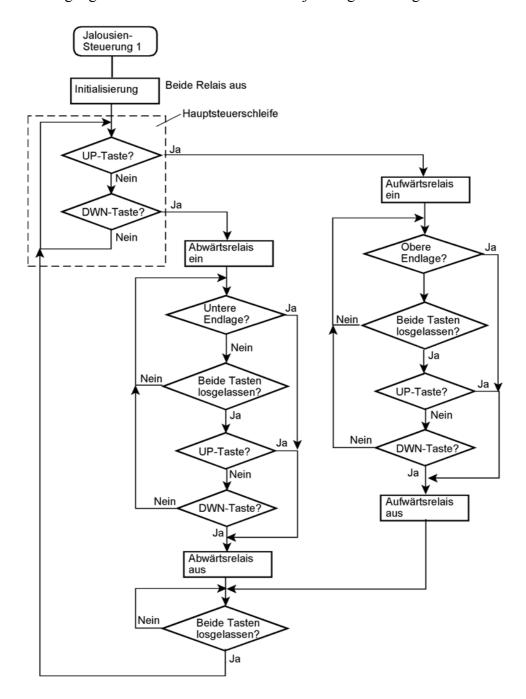

Zu den einfachsten Anwendungsbeispielen gehört das Steuern einer Jalousie. Im Beispiel von Abbildung 1.7 wird ein Gleichstrommotor eingesetzt. Für jede Bewegungsrichtung ist ein Relais vorgesehen, über dessen Kontakte die jeweils entsprechend gepolte Betriebsspannung angelegt wird. Die Endabschaltung erfolgt über mechanisch betätigte Ruhekontakte (Mikroschalter o. dergl.). Die Bewegung der Jalousie wird mit zwei Bedientasten gesteuert.

**Abb. 1.7** Antriebssteuerung mittels Mikrocontroller. 1 - Tasten; 2 - Leistungsstufen; 3 - Aufwärtsrelais; 4 - Abwärtsrelais; 5 - oberer Endlagenkontakt; 6 - unterer Endlagenkontakt.

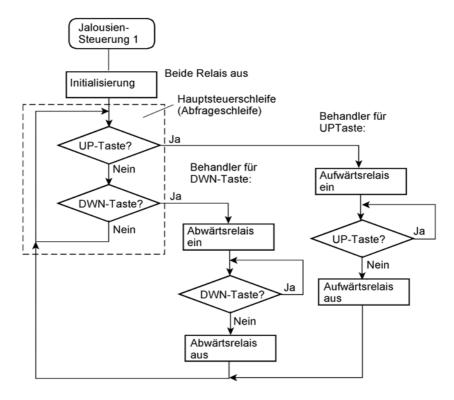

Als erstes soll das wohl einfachste Funktionsprinzip implementiert werden. Solange die Taste UP betätigt wird, läuft der Motor in Aufwärtsrichtung. Solange die Taste DWN betätigt wird, läuft der Motor in Abwärtsrichtung. Erreicht die Jalousie die jeweilige Endlage, wird der zugehörige Ruhekontakt aktiv und unterbricht den Motorstromkreis.

Hierzu braucht man eigentlich gar keinen Mikrocontroller. Simple Drahtverbindungen zwischen den Tastern und den Endlagenkontakten (Mikroschaltern) würden genügen. Trotzdem ist es lehrreich, die Funktionsbeschreibung in einen Programmablauf umzusetzen (Abbildung 1.8). Bereits diesese einfache Flußdiagramm zeigt die typische Programmstruktur aus einer Endlosschleife und den Behandlungsabläufen der einzelnen Funktionen.

Die Endlossschleife (Hauptsteuerschleife, Main Control Loop) fragt ab, was zu tun ist. Ist nichts zu tun, wird sie immer wieder durchlaufen. Ist etwas zu tun, verzweigt sie zum jeweiligen Behandler. Hat der Behandler seine Arbeit beendet, kehrt der Programmablauf zur Hauptsteuerschleife zurück.

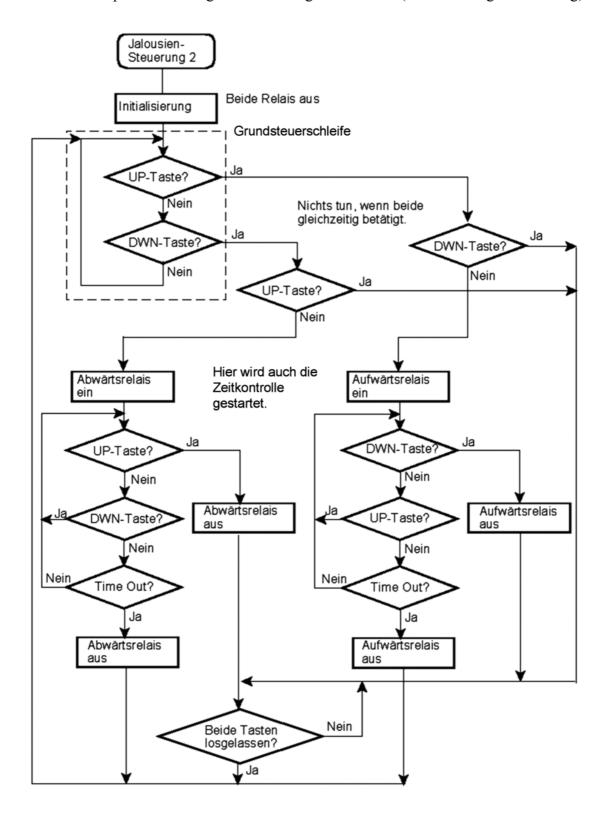

Unschön ist, daß man den Daumen so lange auf der Taste lassen muß, bis die Jalousie die gewünschte Stelle erreicht hat. Sorgen wir also für etwas mehr Bedienkomfort. Ein bloßes Antippen soll genügen. Wenn nichts weiter geschieht, läuft die Jalousie bis zum Endanschlag durch. Um die Bewegung anzuhalten, soll es genügen,die jeweils andere Taste anzutippen. Beispiel: UP antippen – die Jalousie läuft nach oben – DWN antippen – die Jalousie bleibt stehen<sup>3</sup>.

<sup>3:</sup> Das ist die typische Funktionsweise einfacher Jalousiensteuerungen.

**Abb. 1.8** Jalousiensteuerung ganz einfach. Spitzfindigkeiten – beispielweise das Entprellen der Kontakte – wurden hier vernachlässigt.

Diese Funktionsweise ist offensichtlich mit Draht allein nicht zu verwirklichen. Natürlich ginge es mit zusätzlichen Selbsthaltekontakten an den Relais oder mit RS-Flipflops. Solche Alternativen sind aber heutzutage teurer als ein Mikrocontroller. Der Programmablauf ist allerdings komplizierter, als es womöglich auf den ersten Blick aussieht. Das Grundproblem: wie erkennen wir, ob eine Tastenbetätigung eine Bewegung auslösen oder anhalten soll? Abbildung 1.9 veranschaulicht zwei Lösungen. Die eine erledigt das Problem mit einer Zeitkontrolle, die andere, indem sie auch die Endlagenkontakte auswertet<sup>4</sup>.

Hat man sich einmal für den Mikrocontroller entscheiden, ist die Funktionsvielfalt im Grunde unbegrenzt. Weitere Funktionen – so kompliziert sie auch sein mögen – kosten im Grunde nur noch Speicherplatz, also praktisch nichts. Der Funktionsumfang kann unter anderem bis zur ortsabhängigen (astronomischen) Zeitsteuerung<sup>5</sup> und bis zur Fernbedienung übers Internet erweitert werden ...

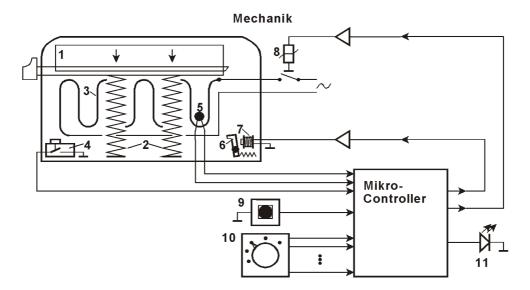

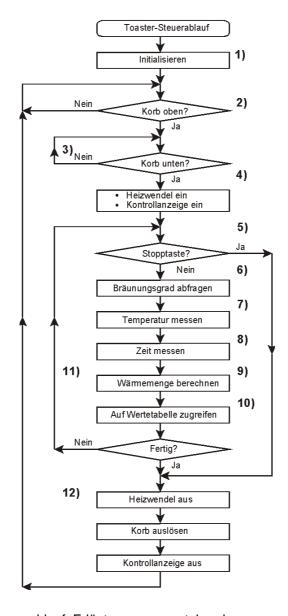

Die Abbildungen 1.10 und 1.11 veranschaulichen ein weiteres Anwendungsbeispiel. Es handelt sich darum, einen Toaster mit einem Mikrocontroller zu steuern.

<sup>4:</sup> Das erscheint als einleuchtende, bessere Lösung, hat aber den Nachteil, daß zusätzliche Leitungen von den Endlagenkontakten zur Steuerung erforderlich sind. Bei Elektroinstallateuren ist so etwas nicht gerade beliebt. Man kann jedoch die Endlage auch auf andere Weise erkennen... (Übungsaufgabe: wie?)

<sup>5:</sup> Öffnen bei Sonnenaufgang, Schließen bei Sonnenuntergang.

Eine erste Tastenbetätigung löst die Bewegung aus. Dabei wird auch eine Zeitkontrolle (Time Out) aktiv. In diesem Zeitintervall kann die jeweils andere Taste die Bewegung anhalten. Das Zeitintervall entspricht näherungsweise der längsten Laufzeit (von Anschlag zu Anschlag).

Hier kann man die Bewegung mit beiden Tasten anhalten. Wird die Jalousie nicht angehalten, endet der Bewegungszustand mit dem Erreichen der jeweiligen Endlage.

**Abb.** 1.9 Jalousiensteuerung mit bescheidenem, aber brauchbarem Bedienkomfort. Der Mikrocontroller muß jetzt erkennen, ob eine nachfolgende Tastenbetätigung die Jalousie anhalten oder erneut in Bewegung setzen soll.

**Abb. 1.10** Die zu steuernde Hardware. 1 - Korb; 2 - Druckfeder; 3 - Heizwendel; 4 - Endlagenkontakt; 5 - Temperatursensor; 6 - Klinke; 7 - Auslösemagnet; 8 - Schaltrelais (oder Triac); 9 - Stoptaste (zum Abbrechen des Toastvorgangs); 10 - Drehschalter zum Einstellen des Bräunungsgrades; 11 - Kontrollanzeige (Leuchtdiode).

Wir legen die Brotscheiben ein und drücken den Korb 1 nach unten. Dort wird er durch die Klinke 6 gehalten. Dieser Betriebszustand wird vom Endlagenkontakt 4 signalisiert. Damit beginnt der Toastvorgang. Um ihn zu beenden, wird der Auslösemagnet 7 erregt und somit die Klinke 6 ausgelöst. Daraufhin drückt die Druckfeder 2 den Korb 1 wieder nach oben. Zur Beeinflussung des Ablaufs sind eine Stoptaste 9 (vorzeitiges Beenden) und ein Drehschalter 10 (zum Einstellen des Bräunungsgrades) vorgesehen. Das Toasten selbst beruht auf einer Erregung der Heizwendel 3. Hierzu wird das Relais 8 angesteuert.

#### Erläuterungen zum Programmablauf:

- 1) Nach dem Einschalten wird alles in die Grundstellung versetzt (Initialisierung). Ist der Korb 1 unten, wird er ausgelöst.

- 2) Der Korb 1 darf nicht (in der unteren Lage) eingerastet sein. Ggf. warten, bis der Endlagenkontakt 4 abgeschaltet hat.

- 3) Warteschleife im Ruhezustand.

- 4) Mit dem Einrasten des Korbes 1 (Meldung über Endlagenkontakt 4) beginnt der Toastvorgang.

- 5) Die Stoptaste 9 wird immer wieder abgefragt, um zu erkennen, ob der Vorgang abgebrochen werden soll.

- 6) Der Drehschalter 10 wird immer wieder abgefragt. Somit kann man den gewünschten Bräunungsgrad auch ggf. mitten im Ablauf ändern (Bedienkomfort).

- 7) Mittels Temperatursensor 5.

- 8) Durch interne Zeitzählung im Mikrocontroller.

- 9) Die bisher umgesetzte Wärmemenge wird aus Temperatur und Zeit errechnet (und in jedem Schleifenumlauf aufsummiert). Es handelt sich hier um eine interne Hilfsgröße, die nicht normgerecht (als SI-Einheit J (Joule)) ermittelt werden muß.

- 10) Das ist ein einfaches, oft angewendetes Prinzip: man rechnet nicht mit komplizierten Formeln, sondern man hat im Mikrocontroller eine Wertetabelle fest gespeichert, die zu jedem einstellbaren Bräunungsgrad die zugehörige Wärmemenge angibt (die Werte wurden während der Entwicklung durch Versuch bestimmt).

- 11) Die Schleife des Toastvorgangs.

- 12) Zurück zur Warteschleife. Hat der Korb die untere Endlage verlassen, kann ein neuer Toastvorgang gestartet werden.

Abb. 1.11 Programmablauf. Erläuterungen vorstehend.

Auch dieses Beispiel zeigt das Organisationsprinzip eines typischen Anwendungsprogramms:

- Es wird gestartet.

- Es richtet sich ein (Initialisierung).

- Es fragt ab, ob etwas zu tun ist.

- Ist etwas zu tun, so wird es ausgeführt (Behandlung der jeweiligen Anforderung).

- Ist die Arbeit erledigt, wird wiederum abgefragt, ob etwas zu tun ist (Abfrageschleife).

# 1.3 Programmentwicklung

# Herkömmliche (prozedurale) Programmierung

Programmieren heißt, eine funktionelle Absicht auf das Ausführen von Anweisungen zurückzuführen, die Bits transportieren (Eingabe, Ausgabe, Laden, Speichern) oder miteinander verknüpfen (Operationen) oder die den Programmablauf beeinflussen (Verzweigungen). Ein Programm ist im Grunde eine Anweisungsfolge. Eine zu steuernde Einrichtung wird kommandiert: führe A aus, dann führe B aus, wenn X, dann führe Y aus, wenn nicht X, dann führe Z aus usw. Die Anweisungen müssen aus einem jeweils vorgegebenen Anweisungsvorrat entnommen werden (Programmiersprache oder Maschinensprache). Sie beziehen sich auf gespeicherte Daten oder auf Schnittstellen der Hardware (Ein- und Ausgabe). Auch die Struktur der Daten entspricht bestimmten Vorgaben (Datentypen).

Diese Programmierweise hat sich auf sozusagen natürlichem Wege ergeben. Die ersten Computer wurden als Rechenmaschinen mit automatischer Steuerung erfunden. Der Maschine ist – wie einem menschlichen Rechner – zu sagen, was sie nacheinander zu tun hat. Ganz am Anfang wurden die Bitmuster der Programme von Hand aufgesetzt. Dann wurden symbolische Maschinensprachen (Assemblersprachen) entwickelt. Schließlich wurden höhere Programmiersprachen geschaffen, um die Programmierarbeit zu erleichtern, den Programmierkomfort zu erhöhen und das Programmieren von den Eigentümlichkeiten der Maschinen unabhängig zu machen. Das Programmieren – gleich mit welchen Sprachmitteln und Entwicklungswerkzeugen – besteht aber stets darin, Prozeduren – also Handlungsanweisungen – zu schreiben, die auf Variable – also Daten – einwirken.

Jedes Programmieren führt – zumindest beim aktuellen Stand der Technik – letzten Endes auf prozedurale Programme, denn es kommen immer Maschinenprogramme heraus, die auf gewöhnlichen Prozessoren laufen.

Wer Aufbau und Wirkungsweise der Prozessoren sowie Feinheiten und Spitzfindigkeiten der Programmabläufe kennenlernen möchte, muß sich auch mit dem prozeduralen – vor allem dem maschinennahen – Programmieren beschäftigen. Deshalb werden wir uns nachfolgend auf diese Art des Programmierens beschränken. Zunächst sollen jedoch einige Alternativen kurz vorgestellt werden.

#### **Objektorientierte Programmierung**

Der Begriff der objektorientierten Programmierung bezeichnet nichts anderes als eine bestimmte Art von Programmierwerkzeugen und -hilfsmitteln. Sie betreffen vor allem die Wiederverwendung, Abwandlung und Weiterentwicklung der Programme sowie das Vermeiden elementarer Programmierfehler. Die anwendungsbezogene Problemlösung ist jedoch nach wie vor im Kopf zu durchdenken und von Hand auszuarbeiten. Und auch beim objektorientierten Programmieren entstehen letzten Endes Maschinenprogramme, die auf gewöhnlichen Prozessoren laufen.

### **Programmgeneratoren und interpretative Systeme**

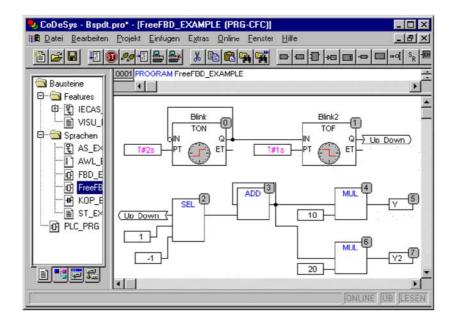

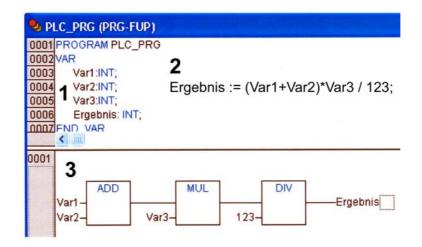

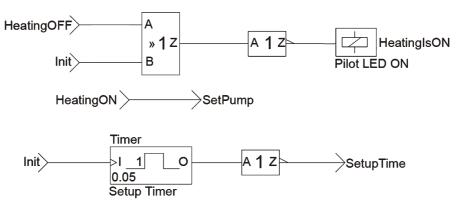

Das herkömmliche Programmieren – in einer Sprache wie C oder gar Assembler – ist zwar von den Grundlagen her nichts weiter als eine Art Kommandieren – also etwas, das sich geradezu von selbst versteht. Es ist aber nicht jedermanns Sache. Die Einarbeitung ist zeitaufwendig; es ist viel zu lernen, und ohne Übung wird es nichts rechtes. Deshalb hat man Programmentwicklungssysteme geschaffen, die es ermöglichen, die Programmierabsicht mit

Beschreibungsmitteln zu erfassen, die im jeweiligen Anwendungsbereich üblich sind. Es sind letzten Endes Struktur- oder Funktionsbeschreibungen. Hiermit kann der Anwender seine Problemlösung selbst formulieren.

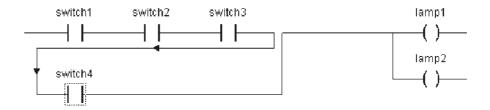

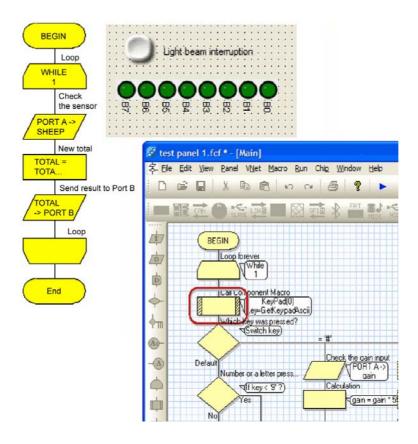

Typische Strukturbeschreibungen beruhen auf Kontaktplänen, Funktionsblöcken oder Schaltsymbolen (Abbildung 1.12 bis 1.15). Typische Funktionsbeschreibungen beruhen auf Flußdiagrammen, Zustandsdiagrammen und Modellierungssprachen (Abbildung 1.16 bis 1.19). Die Beschreibung wird von einem Programmgenerator in einen Programmquelltext umgesetzt oder von einem interpretierenden Programm (Emulator) ausgewertet. Im Bereich der Mikrocontroller wird der Programmgenerator (Code Generator) bevorzugt. Manche Programmgeneratoren erzeugen den Maschinencode direkt. Am weitesten verbreitet ist jedoch der Weg über zwischengeschaltete Sprachebenen. Aus der Beschreibung wird zunächst ein Code in einer höheren Programmiersprache (zumeist in C) erzeugt, der mit einem üblichen Compiler übersetzt werden kann. Manche Entwicklungsumgebungen unterstützen den gesamten Weg, von der Beschreibung über den C-Code, den Assemblercode für den jeweils gewählte Maschine bis hin zum binären Maschinencode. Dieses Verfahren hat zwei Vorteile:

- Compilierte Maschinenprogramme laufen deutlich schneller als eine Emulation (Richtwert: 10 bis 50mal).

- Man kann auf dem Übersetzungsweg eingreifen und den Code (in C oder Assembler) nach eigenen Vorstellungen abwandeln.

## Beschreibungsmittel im Verbund einsetzen

Jedes Beschreibungsmittel ist für bestimmte Arten von Aufgaben besser geeignet als für andere. So nützt ein Zustandsdiagramm nicht viel, wenn Formelausdrücke zu berechnen sind (wie im Beispiel von Abbildung 1.14). Flußdiagramme sind eine anschauliche Darstellung sequentieller Abläufe. Sie sparen aber nur dann Arbeit, wenn man nicht jede Einzelheit graphisch darstellen muß. Deshalb modelliert man mit dem Flußdiagramm nur den grundsätzlichen Ablauf und beschreibt das, was die Blöcke im einzelnen leisten sollen, mit einer Programmiersprache (vergleiche Abbildung 1.18).

## Von Hand programmieren

Manchmal ist die Entwicklungsumgebung zu kostspielig oder für den jeweiligen Prozessortyp nicht verfügbar oder sie reicht nicht aus, um die gesamte Entwurfsaufgabe zu erledigen. Es liegt dann nahe, solche Beschreibungsmittel nur zum Erfassen der Entwurfsabsicht einzusetzen und das eigentliche Programm gleichsam zu Fuß zu erstellen. Flußdiagramme und Funktionspläne können in übliche Programmtexte umgesetzt werden. Kontaktpläne und Zustandsdiagramme führen letzten Endes auf das Ausrechnen Boolescher Ausdrücke und auf elementare Fallunterscheidungen.

Abb. 1.12 Beispiel eines Kontaktplans (IEC61131 KP).

Abb. 1.13 Funktionsblöcke in einer Entwicklungsumgebung (IEC61131 FUP).

**Abb. 1.14** Auf verschiedene Weise programmieren (IEC61131). 1 - Deklaration der Variablen; 2 - Formulierung in der Programmiersprache Structured Text (ST); 3 - Erfassung als Funktionsplan. Die Funktionsblöcke werden gemäß dem Datenfluß hintereinandergeschaltet.

**Abb.** 1.15 Funktionsblöcke und Schaltsymbole in einer anderen Entwicklungsumgebung.

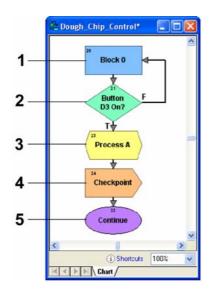

**Abb. 1.16** Eine Entwicklungsumgebung, die auf Flußdiagrammen beruht. Neben den Programmabläufen können auch die Einrichtungen der Ein- und Ausgabe graphisch dargestellt werden, um das Programm am Bildschirm zu simulieren.

**Abb. 1.17** Eine weitere Entwicklungsumgebung auf Grundlage von Flußdiagrammen. 1- Aktionsblock; 2 - Bedingungsblock; 3 - OptoScript-Block; 4 - Prüfpunktblock; 5 - Fortsetzungsblock. OptoScript ist die zum System gehörende Programmiersprache.

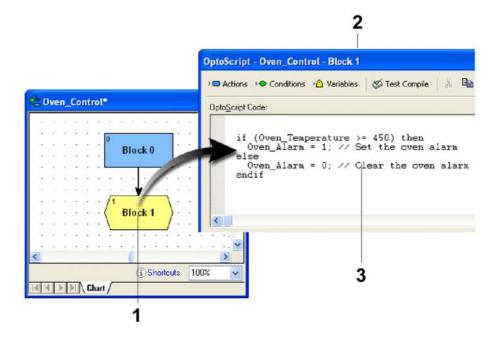

**Abb. 1.18** Was ein Block leisten soll, wird in der zugehörigen Programmiersprache formuliert. 1 - OptoScript-Block; 2 - Editorfenster; 3 - Quelltext des Programmcodes.

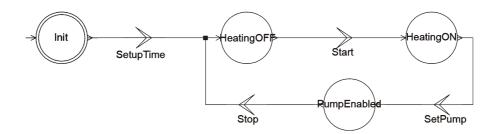

Abb. 1.19 Ein Zustandsdiagramm.

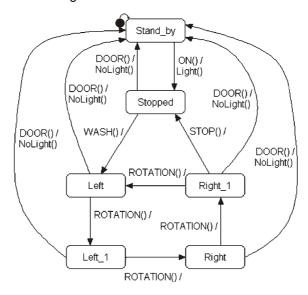

*Abb. 1.20* Ein Zustandsdiagramm in einer Entwicklungsumgebung, die auf der Modellierungssprache UML beruht.

# **Maschinennahe Programmierung**

Maschinennahe Programme werden in der jeweiligen Assemblersprache oder in einer höheren prozeduralen Programmiersprache geschrieben. Die Programmiersprache C wird am häufigsten eingesetzt. C ist im Grunde ein halbwegs maschinenunabhängiger Assembler mit vorgefertigten Kontrollstrukturen und Bibliotheksfunktionen.

Weshalb in Maschinensprache (Assembler) programmieren?

- Es ist in der Praxis nach wie vor erforderlich (Nutzung maschinenspezifischer Besonderheiten, maximale Ausnutzung der Hardware (höchstes Leistungsvermögen oder geringster Aufwand), Umgehung von Unzulänglichkeiten (Workarounds), bis auf den einzelnen Maschinentakt exaktes Zeitverhalten).

- Es vermittelt grundlegendes Erfahrungswissen zum Verstehen, Beurteilen und Auswählen von Prozessorarchitekturen.

#### Ein Volksmärchen:

"C ist eine maschinenunabhängige höhere Programmiersprache. Ein richtig geschriebenes C-Programm läuft auf jeder Maschine. Man muß es nur entsprechend übersetzen." Schön wär's ...

### Die harten Tasachen:

C ist NICHT maschinenunabhängig – vor allem nicht im Bereich der Mikrocontroller. Zudem ist es nicht einmal unabhängig vom Compiler. Der Compiler macht, was er will, und nimmt keine Rücksicht auf subtile Programmierabsichten, wie sie für die Mikrocontrollerprogrammierung typisch sind. Das betrifft u. a.

- die Unterbringung von Variablen in verschiedenartigen Speicherbereichen (SRAM, Flash, EEPROM usw.),

- die Notwendigkeit, auf manche Variable immer wieder zuzugreifen, obwohl sie im Programmverlauf eigentlich nicht verändert wurden (weil es sich um Werte handelt, die von außen oder anderswo her kommen (Eingaben)),

- Befehlsfolgen, die eigentlich nichts berechnen, sondern nur dazu da sind, um Zeit zu verbrauchen.

Da solche Unterscheidungen nicht in den Sprachstandard eingebaut sind, hat sie jeder Compilerautor auf eigene Faust definiert. Selbst bei Beschränkung auf eine einzige Zielarchitektur (z. B. Atmel AVR) entspricht somit jeder Compiler praktisch einem eigenen C-Dialekt. Beim Übergang von Compiler A auf Compiler B muß im Quelltext geändert werden. Wer die Eigentümlichkeiten der jeweiligen C-Umgebung nicht kennt, kann entsprechend geschriebene Quelltexte nicht verstehen. Programmierempfehlungen zur Optimierung hängen sowohl von der Maschinenarchitektur als auch vom Compiler ab<sup>6</sup>.

– C, ohnehin schon häßlich genug, wird noch häßlicher. –

<sup>6:</sup> Zu den wichtigsten Zielen der Entwicklung höherer Programmiersprachen sollte es gehören, daß man Programmabläufe verständlich, wenn nicht gar evident (also von Grund auf einleuchtend) formulieren kann. Im Idealfall ist der Programmtext seine eigene Dokumentation. C ist in dieser Hinsicht besonders schlecht. Gegenbeispiel: Ada. Die Anwendung von Optimierungsempfehlungen, akademischen Weisheiten und Tricks unfehlbarer Gurus macht C-Quelltxete vollends unlesbar. Solche Programme versteht oftmals nur der Urheber – und acht Wochen später auch der nicht mehr...

# C als Mittel zur Gewährleistung der Maschinenunabhängigkeit

In der Theorie schaut alles viel großartiger aus als es wirklich ist. Wenn man wirkliche Maschinenunabhängigkeit haben will, muß man entsprechend entwickeln. Diese Entwicklungsmethodik kostet aber Zeit.

## C als Mittel zur Arbeitserleichterung

Das ist das Hauptmotiv, weshalb man C einsetzt. Man darf sich nur nicht der Illusion hingeben, die Entwicklungsleistung wären maschinenunabhängig und durch einfaches Kompilieren auf xbeliebige andere Maschinen zu übertragen. Deshalb ist es gängige Praxis, bei einer Prozessorachitektur und einer Programmentwicklungsumgebung zu bleiben und deren Nachteile hinzunehmen (zumal professionelle Entwicklungsumgebungen auch richtig Geld kosten<sup>7</sup> – die Annahme, es sei alles umsonst, ist eine irrtümliche ...).

Weshalb nehmen wir eigentlich C? (Es zählen nur vernünftige Gründe.)

- Um schneller voranzukommen.

- Um tatsächlich soweit es irgendwie geht trotz allem maschinenunabhängig zu werden (Portabilität).

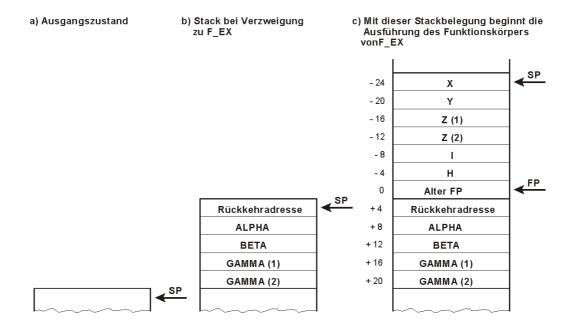

- Der Compiler kümmert sich um

- den Unterprogrammaufruf,

- das Belegen, Retten und Wiedereinstellen von Registern,

- die Speicherbelegung,

- das Adressieren der Variablen,

- die Kontrollstrukturen (Entscheidungen, Schleifen usw.),

- die elementare Arithmetik (= alle vier Grundrechenarten mit den gängigen Datentypen),

- weitere elementare Funktionen (Bibliotheksroutinen), bis hin zu Zeichenketten, Gleitkommazahlen, Winkelfunktionen usw.

Andernfalls – wenn wir von Grund auf alles in Assembler programmieren – müßten wir all dies zu Fuß tun bzw. eigene Lösungen finden.

# Gutgemeinte Empfehlungen:

- 1. Teile und herrsche. Das Problem aufteilen: was ist innere Programmlogik (maschinenunabhängig), was ist echte Ein- und Ausgabe (unvermeidlich maschinenspezifisch), was sind organisatorische Kleinigkeiten (z. B. Speicheraufteilung)?

- 2. Von oben herangehen (Top-Down) und schrittweise verfeinern. Problemlösung zunächst ganz abstrakt nur in C bearbeiten: Variablen Programmlogik Funktionen an den Schnittstellen zur Hardware ("logische" Ein- und Ausgabe).

- 3. Die typische C-Schnittstelle ist ein Funktionsaufruf. Alles,was sich nicht mit standardgemäßem (ANSI-) C ausdrücken läßt, zunächst mit Funktionen erledigen (und wenn diese zunächst bloße Attrappen (Dummies) sind).

- 4. Diese Funktionen schrittweise verfeinern. Wenn erforderlich, durch Assembler-Programmstücke ersetzen. (Notfalls durch Suchen und Ersetzen im Editor.)

- 5. Wenn möglich, Programmlogik auf PC ausprobieren. Funktionskörper ggf. passend abwandeln. Z. B. Eingabe über Tastatur oder Schnittstelle, Ausgabe auf Bildschirm bis hin zur Nachbildung der Peripherie mit Windows-Steuerelementen oder Kombination aus PC und angeschlossener Peripherie-Nachbildung.

<sup>7:</sup> Es geht praktisch nicht ohne Wartungsvertrag. Auch die teuersten Entwicklungssysteme enthalten Fehler...

- 6. Mit C assemblermäßig programmieren. Möglichkeiten der Sprache nicht bis zum Äußersten ausnutzen (Write High-Level, Think Low-Level).

- 7. Man hält sich entweder an akademische Weisheiten oder schreibt Programme, die in endlicher Zeit fertig werden und vernünftig laufen. Keine Angst vor GOTOs, globalen Variablen usw. Der wirkliche Könner ist nicht derjenige, der solche Programmiertechniken ängstlich vermeidet, sondern der weiß, wo man sie einsetzt und wo nicht.

- 8. Compilerspezifische Komfort-Funktionen nicht ausnutzen.

- 9. Systematisch entwickeln.

- 10. Alles richtig dokumentieren. C-Quelltext auch mit Kommentaren ist keine brauchbare Programmdokumentation!

- 11. Das Codieren sollte höchstens 30 % der Programmentwicklungzeit erfordern.

- 12. Erst denken, dann hacken.

- 13. Das Internet weiß nicht alles.

# 1.4 Atmel AVR – das Lehrbeispiel

Die Anfangsgründe der maschinennahen Programmierung und der Rechnerarchitektur gehören zusammen. Beide Wissensgebiete sind keine exakten Wissenschaften. Zwar versucht man sich immer wieder an formalisierten Theorien, aber es ist nach wie vor üblich, in der Lehre mit dem grundsätzlichen Aufbau des Universalrechners und dessen Nutzung zu beginnen. Dabei bezieht man sich meistens auf konkrete Beispiele. Rechnerarchitekturen werden (auch in Hochschullehrbüchern) zumeist ähnlich beschrieben wie Tier- oder Pflanzenarten in der Biologie. Wir verpassen also nicht viel, wenn wir uns tiefgründige Theorien schenken und sofort beginnen, uns in eine bestimmte Architektur einzuarbeiten. Es sollte eine richtige, in der Anwendungspraxis verbreitete Architektur sein; also keine, die eigens zu Lehrzwecken entwickelt wurde. Nur so kann man praxistypische Beschränkungen und Spitzfindigkeiten (Gotchas) am konkreten Beispiel kennenlernen. Die Architektur soll aber auch überschaubar sein; es muß möglich sein, sich in kurzer Zeit einzuarbeiten und nach wenigen Stunden erste Erfolge zu erzielen.

Die AVR-Mikrocontroller der Fa. Atmel haben sich als sehr zweckmäßiger Kompromiß erwiesen. Wichtig ist, wieviel Zeit der Lernende braucht, um vom Zustand der vollkommenen Kenntnislosigkeit bis zum ersten Verständnis und zu ersten Erfolgserlebnissen zu kommen, also zu Programmen, die wirklich laufen. Es gibt einfachere Architekturen. Diese weisen aber stärkere Einschränkungen auf. Man muß zwar weniger Befehle lernen, es sind aber viel mehr Besonderheiten und Spitzfindigkeiten zu beachten. Nun ist auch AVR von Einschränkungen nicht frei. Einige sind sogar SEHR ärgerlich. Es ist aber nicht grundsätzlich schwierig, sich zu behelfen. Andere Mikrocontrollertypen haben ein beträchtlich höheres Leistungsvermögen und eine bei weitem umfangreichere Ausstattung. Sie sind aber auch viel komplizierter. Die Einarbeitung vom Stand Null an ist nicht in wenigen Stunden zu schaffen. Sie kostet mehrere Wochen am Stück (Richt- und Erfahrungswert: wenigstens vier). Um die E-A-Ports eines modernen Hochleistungsprozessors auch nur zu initalisieren, braucht man bereits mehrere Seiten Programmtext. Die E-A-Ports der AVR-Mikrocontroller sind hingegen vergleichsweise einfach. Ihre Wirkungsweise ist leicht zuverstehen, und es genügen einige Programmzeilen, um sie zu initialisieren. Vor allem aber haben sie nicht die häßlichen Nebeneffekte, die die E-A-Ports anderer Mikrocontrollerfamilien aufweisen. Näheres dazu in Abschnitt 4.1.

# 2. Universalrechner

# 2.1 Grundlagen

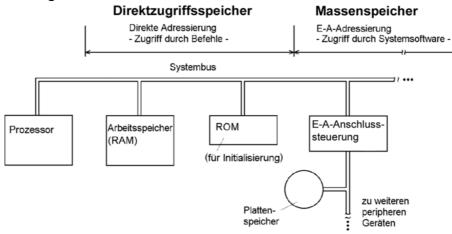

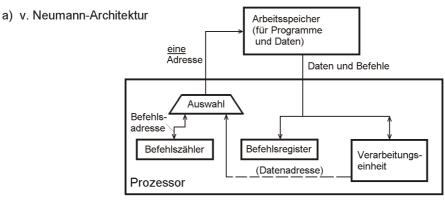

Alle Mikrocontroller und Prozessoren sind programmgesteuerte Universalrechenmaschinen. Betrachten wir diese Begriffe im einzelnen:

- Rechenmaschine: Hauptsache ist das numerische Rechnen, wenigstens in den Grundrechenarten.

- Programmgesteuert: es soll alles automatisch ablaufen.

- Universell: es sollen sich alle überhaupt denkbaren Rechenvorgänge ausführen lassen. Die praktischen Beschränkungen liegen nicht im Grundsätzlichen, sondern in Verarbeitungszeit und Speicherbedarf. Mit anderen Worten: durch Programmieren kann man jeden beliebigen Algorithmus verwirklichen vorausgesetzt, das Programm passt in den Speicher und die Ausführungszeit spielt keine Rolle (unter diesen Voraussetzungen könnte auch der kleinste Prozessor die größten Aufgaben bewältigen).

Die ursprünglichen erfinderischen Ansätze waren zunächst vom Vorgehen eines Menschen angeregt, der komplizierte Rechnungen auszuführen hat. Hierzu ein einfaches Beispiel – eine Formel aus einer Formelsammlung der Elektrotechnik:

$$\mathbf{U}_{\mathbf{A}} = -\mathbf{R}_{\mathbf{G}} \cdot \left( \frac{\mathbf{U}_{1}}{\mathbf{R}_{1}} + \frac{\mathbf{U}_{2}}{\mathbf{R}_{2}} \right)$$

Das Ausrechnen erfordert offensichtlich die folgenden Schritte:

- 1.  $U_1$ :  $R_1$  berechnen. Zwischenergebnis notieren.

- 2.  $U_2$ :  $R_2$  berechnen. Zwischenergebnis notieren.

- 3. Beide Zwischenergebnisse addieren.

- 4. Diesen Wert mit R<sub>G</sub> multiplizieren.

- 5. Das Vorzeichen wechseln.

Es sind also mehrere Rechenoperationen der Grundrechenarten nacheinander auszuführen. Die einfachste Art der Programmsteuerung besteht darin, starre Folgen von Eingaben, Rechenschritten und Ausgaben auszuführen (Abbildung 2.1). Sofern ein hinreichender Vorrat an Rechenoperationen vorgesehen ist, genügt bereits dieses einfache Schema, um viele nicht triviale Anwendungsaufgaben zu lösen.

Wirkliche Universalität ist dann gegeben, wenn:

1. die Reihenfolge der Verarbeitungsschritte in Abhängigkeit von den Verarbeitungsergebnissen abgewandelt werden kann (bedingte Verzweigung),

und

2. die Reihenfolge der auszuführenden Verarbeitungsschritte nicht durch eine unveränderliche Ablaufsteuereinrichtung, sondern durch gespeicherte (und damit beliebig veränderbare oder auswechselbare) Steuerangaben bestimmt wird (speicherprogrammierbare Steuerung).

Abb. 2.1 Komplizierte Berechnungen ausführen – der grundsätzliche Ablauf.

#### **Funktionseinheiten**

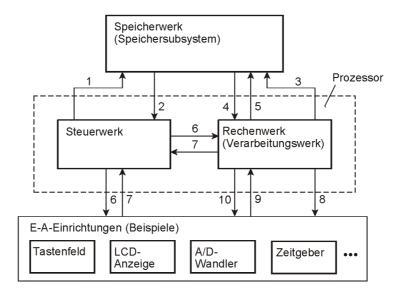

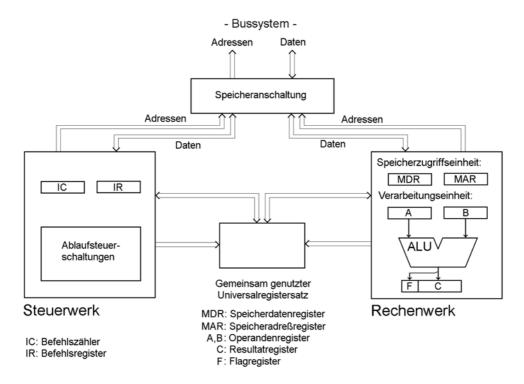

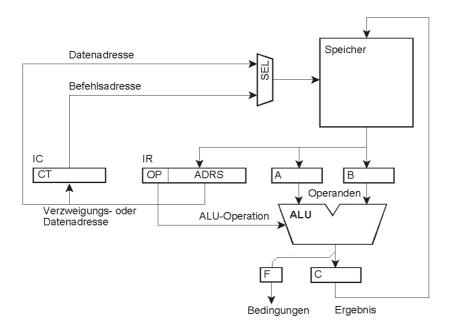

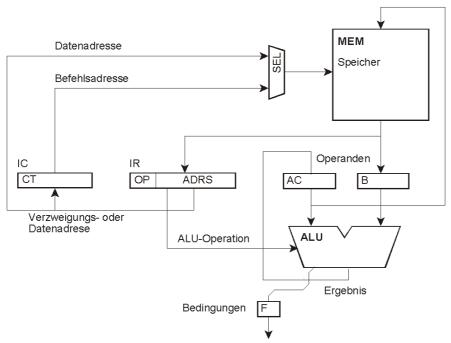

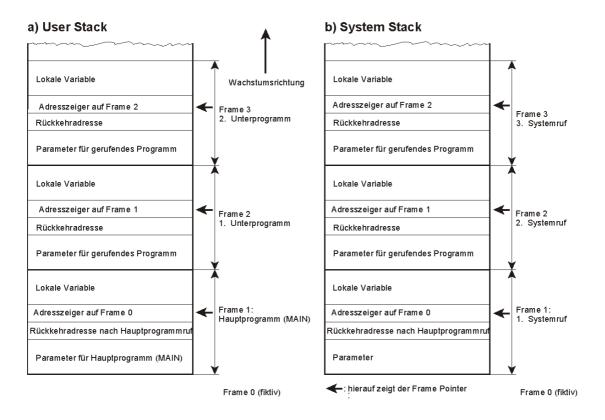

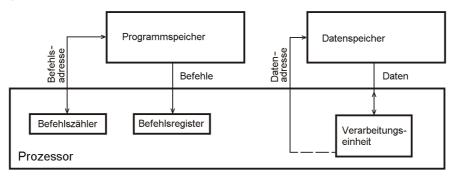

Die grundsätzliche Struktur umfasst vier Funktionseinheiten (Abbildung 2.2):

- 1. Speicherwerk (Speichersubsystem),

- 2. Steuerwerk,

- 3. Rechen- oder Verarbeitungswerk,

- 4. Einrichtungen zur Ein- und Ausgabe (E-A-Einrichtungen).

Das Rechenwerk führt die Rechenoperationen aus. Das Steuerwerk bewirkt, dass die jeweils gewünschten Verarbeitungsschritte nacheinander ausgeführt werden. Das Speicherwerk speichert die zu verarbeitenden Daten (Operanden), die Ergebnisse und die Programme. Die Speicherung erfolgt in Speicherzellen, die über Speicheradressen angesprochen werden. Das Speichersubsystem kann aus verschiedenartigen Speichereinrichtungen aufgebaut sein, die unterschiedliche Speicherkapazitäten, Organisationsformen und Zugriffszeiten aufweisen (Speicherhierarchie). Die E-A-Einrichtungen stellen die Verbindung zur Außenwelt her. Der Verbund von Rechenwerk und Steuerwerk erbringt die eigentlichen Verarbeitungsleistungen. Deshalb wird er als eine einzige Funktionseinheit betrachtet und als Prozessor bezeichnet<sup>8</sup>.

<sup>8:</sup> Andere Bezeichnungen: zentrale Verarbeitungseinheit oder Central Processing Unit (CPU). Das ist heutzutage typischerweise ein einziger Schaltkreis (Mikroprozessor).

**Abb. 2.2** Der Universalrechner im Blockschaltbild. 1 - Befehlsadresse; 2 - Lesen der Maschinenbefehle; 3 - Datenadresse; 4 - Lesen von Daten; 5 - Schreiben von Daten; 6 - Steuersignale; 7 - Bedingungs- und Zustandssignale; 8 - E-A-Adressierung; 9 - Eingabe von Daten; 10 - Ausgabe von Daten.

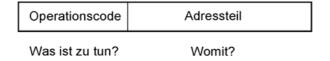

#### Maschinenbefehle

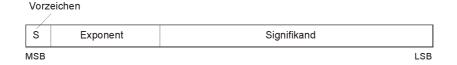

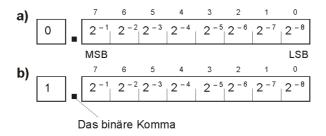

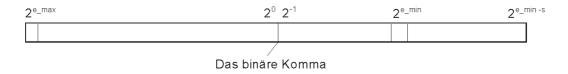

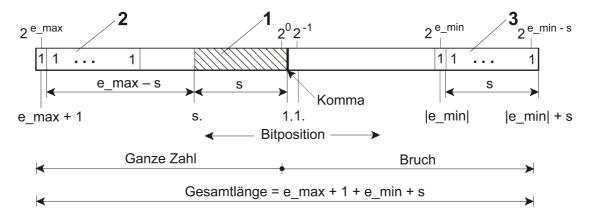

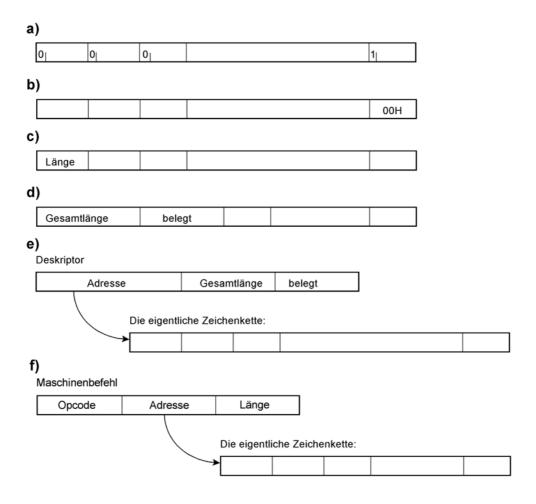

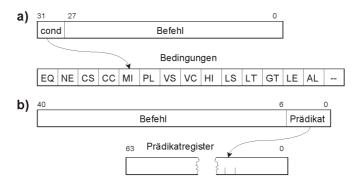

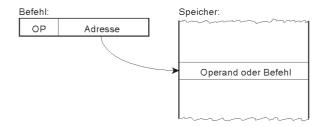

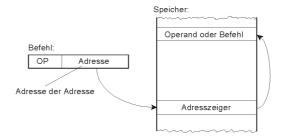

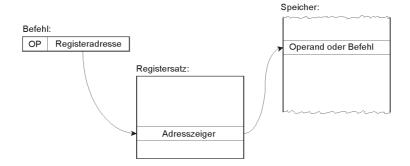

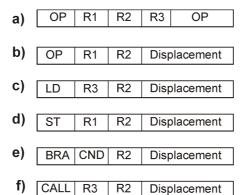

Die Programmsteuerung erfolgt durch gespeicherte Maschinenbefehle. Ein Maschinenbefehl (Abbildung 2.3) beschreibt, was zu tun ist (Operationscode) und womit es zu tun ist (Adressteil). Der Adressteil kann mehrere Adressangaben enthalten Zu einer Zeit wird jeweils ein Maschinenbefehl ausgeführt. Es gibt verschiedene Arten von Maschinenbefehlen:

- Operationsbefehle. Sie weisen Operation an, die vom Rechenwerk ausgeführt wird.

- Transportbefehle. Typische Transportvorgänge sind u. a. die Eingabe, die Ausgabe, das Holen des Inhalts einer Speicherzelle (Lesen) und das Ablegen von Daten in eine Speicherzelle (Schreiben).

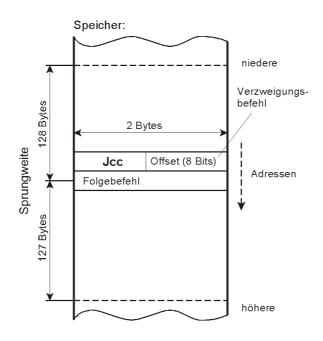

- Verzweigungsbefehle. Sie beeinflussen die Reihenfolge der Befehlsausführung.

- Steuerbefehle. Sie üben Steuerwirkungen aus. Hierzu gehört unter anderem das Einstellen von Betriebsarten.

**Abb. 2.3** Ein Maschinenbefehl. Er beschreibt, was zu tun ist und womit es zu tun ist. In den Einzelheiten der Formatgestaltung und Wirkungsweise gibt es erhebliche Unterschiede.

### Die Befehlsliste (Befehlsvorrat, Instruction Set)

Die Befehlsliste ist das Verzeichnis aller Maschinenbefehle, die ein Prozessor ausführen kann.

#### Was leistet ein Maschinenbefehl?

Ein einzelner Maschinenbefehl kann nur sehr elementare Informationswandlungen oder Steuerungsabläufe veranlassen. Typische Befehlswirkungen sind z. B.:

- das Addieren zweier Binärzahlen.

- das Setzen, Löschen und Abfragen einzelner Bits,

- das Verzweigen zu einem bestimmten anderen Befehl im Programm,

- das Holen oder Abspeichern von einzelnen Binärzahlen, Maschinenworten usw.

Einfache Prozessoren haben um 30...50 verschiedene Maschinenbefehle, Hochleistungsprozessoren typischerweise einige hundert (150...300 sind üblich).

# Einfache und komplexe Befehle – RISC und CISC

Ein Transportbefehl ist – seiner Wirkung nach – offensichtlich einfacher als ein Divisionsbefehl. Es ist eine entscheidende Grundsatzfrage beim Rechnerentwurf, ob man die Befehle auf einfache Wirkungen beschränkt (damit sie schneller ausgeführt werden können und die Maschine nicht zu kompliziert wird) oder ob man Befehle vorsieht, die vergleichsweise komplexe Funktionen auslösen (damit es die Programmierer leichter haben). Die pauschale Einteilung in einfache und komplexe Befehle wird durch zwei Marketingbegriffe ausgedrückt:

- CISC = Complex Instruction Set Computer. Die Befehlswirkungen sind vergleichsweise komplex. Manche Befehlswirkungen umfassen sowohl Transport- als auch Verarbeitungsfunktionen. Es gibt viele Befehle und Befehlsformate. Typische Beispiele: 8051, Z 80, 68k/Coldfire, 8086 und alle Weiterentwicklungen bis hin zu den Prozessoren der Personalcomputer.

- RISC = Reduced Instruction Set Computer. Die Befehlswirkungen sind vergleichsweise elementar. Transport- und Verarbeitungsfunktionen sind voneinander getrennt (Load/Store-Prinzip). Es gibt nur wenige Befehlsformate. Die meisten Befehle sind gleich lang. Typische Beispiele: PIC, AVR, V850, ARM, MIPS, SPARC, PowerPC.

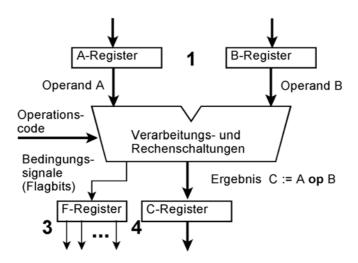

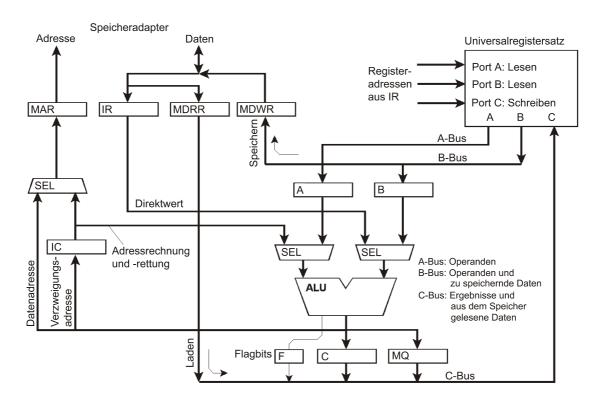

#### **Das Rechenwerk**

Das Rechenwerk eines typischen universellen Prozessors besteht aus der Speicherzugriffseinheit und der Verarbeitungseinheit.

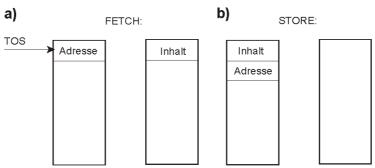

Die Speicherzugriffseinheit dient dazu, die Operanden aus dem Speicher zu holen und die Ergebnisse abzuspeichern. Ein einfache Speicherzugriffseinheit enthält ein Speicheradreßregister, wenigstens ein Speicherdatenregister (oder zwei, eines zum Lesen und eines zum Schreiben) sowie die zugehörigen Steuerschaltungen.

Die Verarbeitungseinheit dient dazu, die Informationswandlungen auszuführen, die von den Maschinenbefehlen angewiesen werden. Die Operanden und Ergebnisse sind Bits oder Bitketten (beispielsweise Bytes oder Maschinenwörter). Die einfachste Form der Informationswandlung ist die kombinatorische Verknüpfung. Typischerweise werden zwei Operanden miteinander verknüpft, um ein einziges Ergebnis zu bilden (vgl. die Grundrechenarten):

$$C := A \text{ op } B$$

Das Ergebnis kann durch zusätzliche Bedingungssignale (Flagbits) ergänzt werden. Weitere Abwandlungen:

- nur ein Operand,

- mehr als zwei Operanden,

- mehr als ein Ergebnis,

- keine Bedingungssignale, sondern nur Ergebnisse,

- keine Ergebnisse, sondern nur Bedingungssignale,

- nur eine einzige Operation (Einzweckschaltung),

- mehrere auswählbare Operationen,

- mehrere Operationen, die gleichzeitig ausgeführt werden,

- feste Formate (Wortlänge, Verarbeitungsbreite),

- wählbare oder einstellbare Formate.

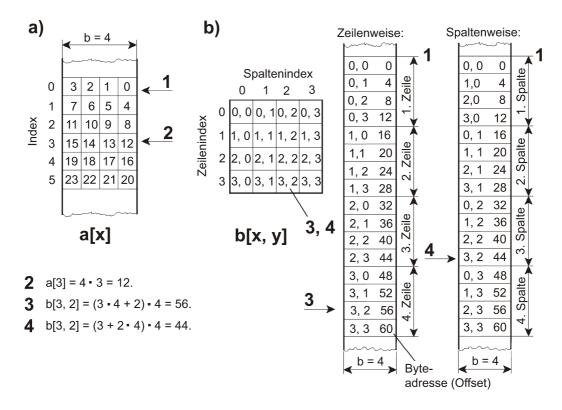

Operanden und Ergebnis werden in Registern gehalten. Dazwischen liegen die konmbinatorischen Verknüpfungsschaltungen (Abbildung 2.4). Aus der Erfahrung heraus hat sich eine Menge von besonders zweckmäßigen elementaren Operationen ergeben, die in nahezu allen Prozessorarchitekturen vorgesehen sind. Je nachdem, ob die Operanden als Binärzahlen oder als Bitketten behandelt werden, unterscheidet man aritmetische und logische Operationen. Die elementaren Operationen des typischen Universalprozessors umfassen Datentransporte, bitweise Boolesche Verknüpfungen, Verschiebeoperationen und – als komplizierteste dieser Operationen – die Addition zweier Binärzahlen<sup>9</sup>; die Verarbeitungseinheit<sup>10</sup> ist gleichsam um den Binäraddierer (Adder) herumgebaut.

*Abb. 2.4* Eine Verarbeitungseinheit. 1 - Operandenregister; 2 - Ergebnisregister; 3 - Bedingungsregister (Flagregister, Zustandsregister).

# **Das Steuerwerk**

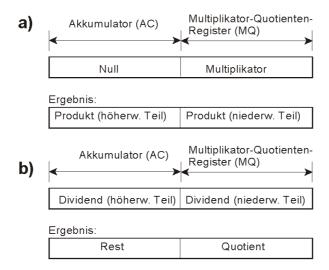

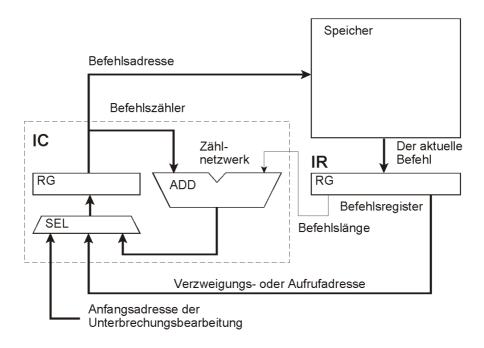

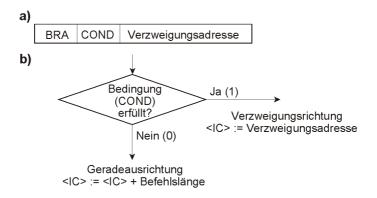

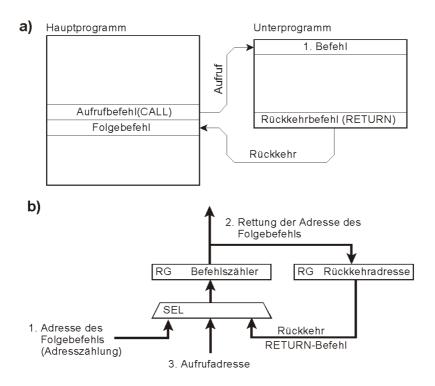

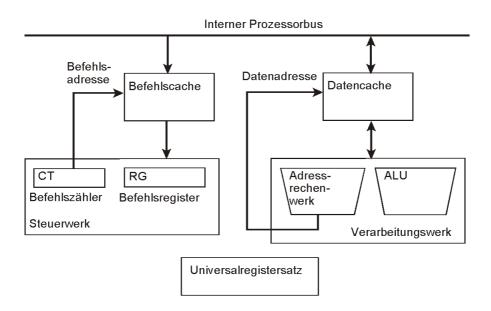

Das Steuerwerk hat die Aufgabe, die Befehle aus dem Speicher zu holen, die Befehlsbitmuster zu decodieren, Steuersignale an die anderen Einrichtungen zu lieferen und Zustandsmeldungen dieser Einrichtungen auszuwerten. Die üblichen Prozessoren lesen die Befehle nacheinander von aufeinander folgenden Speicheradressen. Die jeweilige Befehlsadresse wird durch einen Zählvorgang gewonnen (Befehlszähler, Instruction Counter IC). Ist eine Verzweigung auszuführen, wird der Befehlszähler mit der Verzweigungsadresse überladen. Der aus dem Speicher gelesene Befehl wird in ein Befehlsregister (Instruction Register IR) geladen, dem die Decodier- und Ablaufsteuerschaltungen nachgeordnet sind.

<sup>9:</sup> Die Maschinenoperationen können gar nicht allzu kompliziert sein, denn es muß möglich sein, eingermaßen kostengünstige Schaltungen zu bauen, um sie auszuführen.

<sup>10:</sup> Andere Bezeichnungen: Operationswerk, Arithmetik-Logik-Einheit, Arithmetic/Logic Unit (ALU).

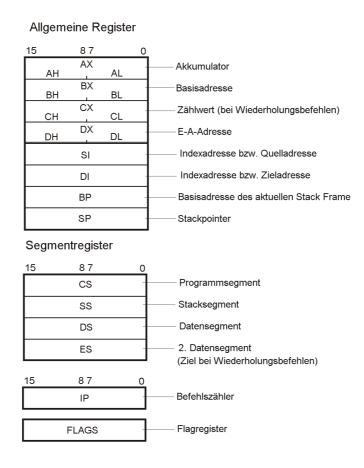

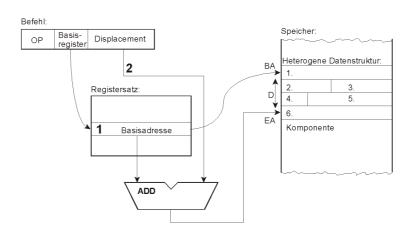

### Die Register

Register sind jene Speichermittel, die direkt mit den kombinatorischen Schaltungen verbunden sind. Sie bestehen aus Latches oder Flipflops (vgl. Digitaltechnik). In der Architektur – und damit beim Programmieren – sind nur jene Register von Bedeutung, die programmseitig zugänglich sind (Registermodell der Architektur). Man kann die Architektur auch ganz ohne Register auslegen (natürlich enthält die Hardware welche, nur merkt der Programmierer nichts davon<sup>11</sup>). Es hat sich aber bewährt, eine gewisse Anzahl an Registern dem Programmierer zugänglich zu machen. Sie dienen als Speicher mit sehr kurzer Zugriffszeit. Die Auslegung als sog. Universalregister (General Purpose Registers) hat sich als besonders zweckmäßig erwiesen. Jedes dieser Register kann wahlweise als Speicher für Variable und Ergebnisse oder als Adreßregister verwendet werden. Abbildung 2.5 zeigt das Blockschaltbild eines typischen Universalprozessors, der mit einem Universalregistersatz ausgerüstet ist.

Abb. 2.5 Ein Universalprozessor.

#### Architektur

Dieser pauschale Allerwelts- und Allgemeinbegriff bezeichnet in der Informatik nichts anderes als die Ausgestaltung wohldefinierter Schnittstellen. Um eine Architektur zu nutzen, braucht man nur die Schnittstellendefinition zu kennen und kann alle Fragen des inneren Aufbaus vernachlässigen. So spricht man von der Architektur eines Computers, eines Prozessors, eines Netzwerks, eines Betriebssystems usw. Die Rechnerarchitektur (Computer Architecture) betrifft die Schnittstelle zwischen Hardware und Software; sie beschreibt Aufbau und Wirkungsweise des Computers aus der Sicht des Programmierers. Die wichtigsten Architekturmerkmale umfassen die Wortlänge, den Befehlsvorrat, den Registersatz und die Adressierungsvorkehrungen.

<sup>11:</sup> Man spricht dann davon, daß diese Register implizit genutzt werden.

# Programmiermodelle

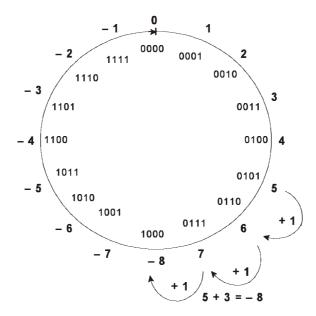

Das Programmiermodell<sup>12</sup> (Programming Model) ist das Erscheinungsbild der Architektur aus der Sicht des Programmierers. Es ergibt sich aus den Architekturmerkmalen und den grundsätzlichen Vorgaben zu deren Nutzung. Manche Architekturen gestatten es, zwischen verschiedenen Programmiermodellen zu wählen (typische Beispiele sind die ARM-Prozessoren und die Prozessoren der Personalcomputer). Viele Merkmale der Universalrechner haben sich aus den technischen Bedingungen der Anfangszeit heraus ergeben. Im Laufe der Entwicklungsgeschichte sind sie zu Industriestandards geworden, die man in allen anwendungspraktisch bedeutsamen Rechnerarchitekturen wiederfindet:

- die binäre Arbeitsweise,

- der adressierbare Speicher,

- die Binärzahl als elementare Datenstruktur,

- die Zweierkomplementarithmetik,

- bestimmte elementare Formate, z. B. Datenstrukturen von 4, 8, 16, 32 usw. Bits Länge,

- die Auslegung der elementaren (adressierbaren) Speicherzellen (Byte- oder Wortadressierung),

- die grundsätzlichen Befehlswirkungen.

# Anwendungsprogrammschnittstelle (API)

Als Anwendungsprogrammschnittstelle oder API (Application Programming Interface) bezeichnet man Schnittstellen, die dazu dienen, andere Programme oder Funktionseinheiten der Hardware vom Anwendungsprogramm aus anzusprechen. Eine API ist nichts Körperliches, sondern eine Art Dienstvorschrift zum Aufrufen der jeweiligen Funktionen. Ein (stark vereinfachtes) Beispiel: Um ein Zeichen zu drucken, übertrage zunächst die laufende Nummer des gewählten Druckers, dann das Druckkommando und dann den Zeichencode. Ist das Zeichen gedruckt, kommt ein Zustandsbyte zurück. Enthält es den Wert Null, ist alles o.k. Ansonsten hat sich ein Fehler ergeben, zu dem der zurückgegebene Wert nähere Angaben enthält.

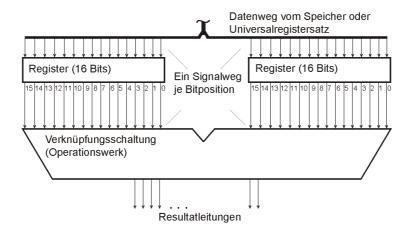

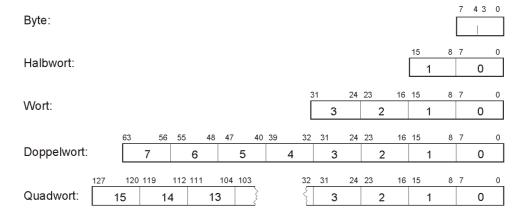

## Maschinenwort und Verarbeitungsbreite

Das Maschinenwort ist eine Aneinanderreihung von Bitpositionen. Es ist im Grunde ein Behälter für typische Datenstrukturen, die von den Maschinenbefehlen angesprochen werden können. Die Wortlänge ist einer der ganz grundsätzlichen Architekturkennwerte. Das Wort ist die Datenstruktur, für die die jeweilige Architektur von Grund auf ausgelegt ist. Typische Wortlängen moderner Prozessoren betragen 8, 16, 32 und 64 Bits. In diesem Sinne spricht man von einer 8-Bit-Architektur, von einer 16-Bit-Architektur usw.

Die Verarbeitungsbreite wird in Bits angegeben. Der Kennwert bringt zum Ausdruck, wie lang eine elementare Datenstruktur ist, die im Prozessor auf einmal (mit allen Bitpositionen gleichzeitig in einem Taktzyklus) transportiert oder verarbeitet werden kann (Abbildung 2.4). Moderne universelle Prozessoren haben Verarbeitungsbreiten von 4, 8, 16, 32 oder 64 Bits. Spezialprozessoren und Beschleunigungszusätze haben bisweilen noch größere Verarbeitungsbreiten (z. B. 128 oder 256 Bits).

Die Wortlänge ist ein Kennwert der Architektur, die Verarbeitungsbreite ein Kennwert der Schaltung.

<sup>12:</sup> Ein Modell ist hier keine verkleinerte und vereinfachte Nachbildung. Das Wort ist vielmehr ein Allgemeinbegriff für Prinziplösungen, grundsätzliche Ausführungsformen usw., wobei tiefere Einzelheiten vernachlässigt werden.

Abb. 2.6 Zur Erklärung der Verarbeitungsbreite.

*Wortlänge* = *Verarbeitungsbreite?*

Die Gleichsetzung liegt nahe. Sie ist auch der heutzutage typische Stand der Technik (eine 32-Bit-Architektur wird schaltungstechnisch mit einer Verarbeitungsbreite von 32 Bits implementiert usw.). Das ist aber nicht immer der Fall. Manchmal ist die Verarbeitungsbreite geringer als die Wortlänge. Dann sind mehrere Taktzyklen erforderlich, um ein Wort zu transportieren oder zwei Wörter miteinander zu verknüpfen. Ist die Verarbeitungsbreite größer, ist es möglich, mehrere Wörter gleichzeitig zu transportieren und zu verarbeiten (Parallelverarbeitung).

#### Maschinenwort und Befehlsformat

Wenn man eine Prozessorarchitektur entwirft, ist – in dieser Hinsicht – zweierlei festzulegen:

- 1. Der Funktionsumfang. Welche Operationen und Abläufe sollen von den Befehlen ausgelöst werden? Damit ordnet sich die Maschine in eine bestimmte Leistungsklasse ein.

- 2. Die Befehlsformate. Wie werden die Befehle binär codiert?

Jedes Befehlsformat ist ein Kompromiß. Nun kann man sich eine – auf den ersten Blick – kompromißlose Auslegung vorstellen: jeder Befehl ist so lang, wie es jeweils nötig ist, um alle Angaben (Adressen, Direktwerte usw.) unterzubringen, die zur Ausführung der jeweiligen Funktion benötigt werden (variable Befehlslänge). Es ist aber trotzdem ein Kompromiß, und zwar zugunsten des Programmierkomforts auf Kosten der Kompliziertheit (vor allem der Steuerung). In Mikrocontrollern kann man sich diese Kompliziertheit nicht leisten. Deshalb werden die Befehle fest formatiert. Typische Befehlslängen entsprechen einem halben Maschinenwort, einem Maschinenwort oder zwei Maschinenwörtern. Man bekommt aber nicht immer alles unter, was man zur Ausführung einer bestimmten Funktion benötigt. Solche Funktionen müssen dann mit mehreren Befehlen erledigt werden. Aus der Absicht, mit kurzen Befehlen auszukommen (Schaltungsaufwand, Speicherkapazität) ergeben sich mehr oder weniger ärgerliche Einschränkungen und der Zwang, manchmal ein simple Programmierabsicht mit mehreren Befehlen auf geradezu hanebüchen trickreiche Weise ausprogrammieren zu müssen<sup>13</sup>.

### Der Adreßraum

Dieser Begriff bezeichnet die Menge der jeweils adressierbaren Speicherzellen, E-A-Anschlüsse, Register usw. Man spricht dann sinngemäß vom Speicheradreßraum, E-A-Adreßraum usw. Eine

<sup>13:</sup> Auch der Atmel AVR ist von solchen Einschränkungen und dem Zwang zur Trickprogrammierung nicht frei. Also nicht ärgern, nur wundern...

Adreßraumangabe ist nichts im wörtlichen Sinne Räumliches, sondern eine bloße Zahl, die besagt, wieviele Elemente überhaupt einzeln adressierbar sind.

Einer Adresse von n Bits Länge entspricht ein Adreßraum von  $2^n$  Elementen. Bei einer 20-Bit-Speicheradresse umfasst der Speicheradreßraum  $2^{20} = 1\,048\,576$  einzeln adressierbare Speicherzellen.

### Adressierungsvermögen

Der Begriff entspricht im Grunde dem des Adreßraums, wird aber in einem etwas anderen Sinne verwendet: wird eine Adresse mit einer Länge von n Bits ausgelegt, so wird damit ihr Adressierungsvermögen (Addressing Capability) auf 2<sup>n</sup> adressierbare Datenstrukturen eingeschränkt. Tabelle 2.1 gibt einen Überblick über typische Adreßlängen und deren Adressierungsvermögen.

### Wozu immer mehr Adreßbits?

Grundsätzlich kann man mit jedem Prozessor – sofern er als wirklicher Universalrechner ausgelegt ist – jede Verarbeitungsbreite und jede Adressierungsweise nachbilden, und zwar mittels Software und (erforderlichenfalls) externer Zusatzbeschaltung. So könnte man z. B. eine 64-Bit-Architektur (64 Bits Verarbeitungsbreite, 64-Bit-Adressierung) mit einem 8-Bit-Prozessor realisieren – es würde funktionieren, wäre aber recht langsam. Der Übergang auf immer mehr Bits wird vor allem durch Forderungen seitens der Adressierung vorangetrieben. Dass man einzelne Bytes adressieren kann, gehört zum Stand der Technik. Lange Zeit war es weit mehr als ausreichend, jedes von rund vier Milliarden Bytes auswählen zu können (32-Bit-Adresse). So große Speicher konnte man über Jahrzehnte hinweg gar nicht bauen. Zwischenzeitlich sind aber auch die Datenmengen ins Gigantische gewachsen. Beispielsweise fallen bei der digitalen Speicherung eines Spielfilms zunächst mehrere Millionen Bytes je Sekunde an. Nun möchte man derartige Videodaten zunächst "roh" speichern und dann mit Software nachbearbeiten. Hierzu ist es aber notwendig, jedes Byte einzeln auswählen (= adressieren) zu können. Es lässt sich leicht überschlagen, dass z. B. ein Film von zwei Stunden Spieldauer mehr Bytes umfasst, als mit einer 32-Bit-Adresse auswählbar sind (beispielsweise ergeben 7200 s zu je vier Millionen Bytes rund 29 Milliarden Bytes). Aber auch die Weiterentwicklung der traditionellen Datenverarbeitung führt auf riesige Datenmengen – man möchte einfach alles speichern, was anfällt, um dann Stoff zum Auswerten zu haben (Data Warehousing, Data Mining). Ebenso muss ein Server, der eine gutsortierte Internet-Site bedient, mit derartigen Datenmassen umgehen können.

| Adresslänge | Adressierbare Bytes                                                                  | Anmerkungen                                                                   |

|-------------|--------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| 8 Bits      | $2^8 = 256$                                                                          | Meist zu wenig. Viele 8-Bit-Prozessoren haben 16-Bit-Adressierung             |

| 16 Bits     | $2^{16} = 65\ 536 = 64\ k$                                                           | Oftmals zu wenig. Viele 16-Bit-Prozessoren haben 20- oder 24-Bit-Adressierung |

| 32 Bits     | $2^{32} = 4\ 294\ 967\ 296\ 4\ G \approx 4\ Milliarden$                              | Ein typischer Industriestandard                                               |

| 36 Bits     | $2^{36} = 68719476736 = 64 G \approx 68$<br>Milliarden                               | Adresserweiterung verschiedener PC-<br>Prozessoren                            |

| 40 Bits     | $2^{40} = 1\ 099\ 511\ 627\ 776 = 1\ T\ \approx 1$<br>Billion = 1000 Milliarden      | Technisches Adressierungsvermögen vieler 64-<br>Bit-Typen                     |

| 48 Bits     | $2^{48} = 281 \ 474 \ 976 \ 710 \ 656 = 256 \ T$<br>$\approx 280 \ \text{Billionen}$ | Eine heutzutage bei weitem ausreichende<br>Grenze des Adressierungsvermögens  |

| Adresslänge | Adressierbare Bytes                                                                                            | Anmerkungen                                           |

|-------------|----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 64 Bits     | $2^{64} = 18\ 446\ 7444\ 073\ 709\ 551\ 616 = 16$<br>E $\approx 18\ Trillionen = 18\ Milliarden$<br>Milliarden | Der Industriestandard im obersten<br>Leistungsbereich |

(k = Kilo, M = Mega; T = Tera; E = Exa)

Tabelle 2.1 Adresslänge und Adressierungsvermögen.

# **Typische Verarbeitungsbreiten**

#### 1 Bit

Bitseriell arbeitende Maschinen sind in der heutigen Praxis bedeutungslos. 1-Bit-Prozessoren sind keine Universalrechner, sondern Spezialprozessoren für Steuerungsaufgaben (Bitprozessoren, Programmable Logic Controllers (PLCs)). Sie haben eigentlich nur historische Bedeutung als Vorläufer der modernen speicherprogrammierbaren Steuerungen (SPS). Die seinerzeit gefundenen Lösungen können aber als Anregungen dienen, wenn programmierbare Steuerschaltungen zu entwerfen sind.

#### 4 Bits

Eine Verarbeitungsbreite von vier Bits kommt offensichtlich mit besonders geringen Aufwendungen aus. Diese Verarbeitungsbreite ist durchaus angemessen, wenn nur mit binär codierten Dezimalzahlen oder gar nicht zu rechnen ist (Steuerungsaufgaben usw.). 4-Bit-Maschinen sind ungeeignet, wenn umfangreichere Adressrechungen auszuführen sind. Sie eigenen sich nur für algorithmisch einfache Aufgaben. Typische Einsatzbereiche sind Zeitrelais, Schaltuhren, Haushaltgeräte, Spielzeuge und LCD-Anzeigen. Manche Hersteller haben 4-Bit-Schaltkreise für solche Einsatzfälle nach wie vor im Fertigungsprogramm<sup>14</sup>. Diese Verarbeitungsbreite kann auch in Eigenentwicklungen von Vorteil sein. Der Ressourcenbedarf (Datenwege usw.) ist gering, und es ist möglich, alle Verknüpfungen von zwei 4-Bit-Operanden mit Zuordnerspeichern zu erledigen, bis hin zu Additions- und Subtraktionstabellen und zum kleinen Einmaleins.

### 8 Bits

Die meisten der kleinen Mikrocontroller haben eine Verarbeitungsbreite von acht Bits. Für viele Anwendungen reicht das Leistungsvermögen vollauf aus – nicht selten auch bei naiver Hochsprachenprogrammierung, also ohne leistungssteigernde Tricks, maschinenspezifische Anpassungen im Quelltext und optimierende Compiler. Die Grenzen liegen vor allem im Adressierungsvermögen und in der Adressrechnung. Die meisten Architekturen sind auf 16 Adressbits beschränkt (64 kBytes). Eine Adressverlängerung ist manchmal vorgesehen. Deren Nutzung ist aber vergleichsweise mühevoll – man muss beim Programmieren schon mitdenken. Praxistipp: Wenn man einen größeren Adressraum braucht, ist es oftmals besser, eine von Grund auf entsprechend großzügig ausgelegte Architektur zu wählen. Dann muss man sich nicht mit Speicherbereichen, Bankregistern usw. abmühen.

### 16 Bits

Die Verarbeitungsbreite kommt vor allem dann zur Wirkung, wenn umfangreichere Berechnungen auszuführen sind. Acht Bits sind zur Darstellung von Messwerten usw. oftmals

<sup>14:</sup> Dass man nur noch die laufende Massenfertigung im Blick hat, ist u. a. daran zu erkennen, dass keine Starterkits und Entwicklungsumgebungen angeboten werden.

zu wenig, weil die Auflösung zu gering ist (rund 0,4 % vom Endwert). Viele Analog-Digital-Wandler haben 10 Bits und mehr (Auflösung bei 10 Bits rund 0,01 %, bei 14 Bits rund 0,006 % vom Endwert). Eine Verarbeitungsbreite von 16 Bits reicht aus, um solche Werte darzustellen. Sie genügt aber zumeist nicht als Speicheradresse. Die meisten 16-Bit-Architekturen haben längere Adressen. Praxistipp: Beim Auswählen von 16-Bit-Prozessoren vor allem auf die Vorkehrungen zur Adressverlängerung und Adressrechnung achten. In dieser Hinsicht kann es grundsätzliche Unterschiede geben, die sich bis in die Anwendungsprogrammierung und die Compiler hinein bemerkbar machen. Als Beispiele seien die Architekturen x86 und 68k genannt (x86: 20 Adressbits und Segmentierung; 68k: 24 Adressbits und linearer Adressraum).

#### 32 Bits

Die Verarbeitungsbreite ist für die weitaus meisten Anwendungen vollauf ausreichend – auch für die Adressrechnung. Eine Adressverlängerung ist zumeist unnötig. Die meisten Mikrocontroller und Plattformen der oberen Leistungsbereiche beruhen auf RISC-Prozessorkernen mit 32 Bits Verarbeitungsbreite. Die 32-Bit-Schaltkreise haben im Grunde nur einen manchmal schwerwiegenden anwendungspraktischen Nachteil – nämlich extrem miniaturisierte Gehäuse mit vielen Anschlüssen, die auf herkömmliche Weise (Zweiebenenplatinen, Schwalllöten usw.) nicht zum Einsatz zu bringen sind. Deshalb ist man oftmals auf fertige Plattformen angewiesen.

#### 64 Bits

Solche Prozessoren sind vor allem entwickelt worden, um das Adressierungsvermögen zu erweitern. Darüber hinaus ergibt sich aufgrund der Verarbeitungsbreite eine allgemeine Leistungssteigerung. Sie kommt vor allem dann zur Wirkung, wenn tatsächlich mit so langen Datenstrukturen gearbeitet wird. Sind die Datentypen kürzer (32-Bit-Binärzahlen, Bytes usw.) ergibt ein Verdoppeln der Verarbeitungsbreite aber keineswegs eine doppelt so hohe Verarbeitungsleistung.

# Das Leistungsvermögen der Prozessoren

Der einzig wirklich wahre Leistungskennwert ist die tatsächliche Ausführungszeit für die jeweilige Anwendungsaufgabe. Demgemäß wäre das einzig brauchbare Bewertungsverfahren das Ausprobieren. Zumeist geht es aber darum, sich zu Beginn eines Entwicklungsvorhabens für eine bestimmte Grundsatzlösung zu entscheiden und die wichtigsten Bauelemente auszuwählen. Aufwendige Vorversuche oder gar mehrere Anläufe wird man sich kaum leisten können. Deshalb muss man sich an pauschalen Kennwerten orientieren.

#### Datenblattkennwerte

Datenblätter enthalten Geschwindigkeits- oder Zeitangaben für die einzelnen Abläufe. Von besonderer Bedeutung sind die Befehlsausführungszeiten und die Latenzzeiten der Unterbrechungsbehandlung. Typische pauschale Leistungskennwerte sind

- die Anzahl der Taktzyklen je Befehl (Cycles per Instruction, CPI),

- die Anzahl der Befehle, die gleichzeitig ausgeführt werden (Instruction Level Parallelism, ILP),

- die Anzahl der Befehle, die in einem Taktzyklus ausgeführt werden (Instructions per Cycle, IPC).

- die Anzahl der ausgeführten Befehle in der Sekunde (Instructions per Second, IPS). Dieser Wert ist die Verarbeitungsleistung. Mit entsprechenden Vorsätzen ergeben sich die in Marketingkreisen so beliebten MIPS und FLOPS.

Die meisten Prozessoren sind Einzelprozessoren. Sie können zu einer Zeit nur einen Befehl ausführen (ILP = 1). Leistungsfähigere Typen haben mehrere Verarbeitungswerke (Superskalarprozessoren), um mehrere Befehle gleichzeitig auszuführen (ILP > 1). CPI = 2 und ILP = 4 bedeuten, dass zur Ausführung eines Befehls zwei Taktzyklen erforderlich sind und dass vier Befehle gleichzeitig ausgeführt werden. Aus CPI und ILP kann man die Anzahl der Befehle je Taktzyklus als fiktive Größe IPC errechnen:

$$IPC = \frac{ILP}{CPI}$$

(1.1)

Zunächst soll angenommen werden, diese Werte seien konstant (alle Befehle erfordern gleich viele Takte, und es werden immer gleich viele Befehle parallel ausgeführt).

## Die Programmausführung

Während der Ausführungszeit  $t_{EX}$  eines Programmablaufs werden in  $n_{C}$  Taktzyklen mit der Taktzykluszeit  $t_{C}$   $n_{I}$  Befehle ausgeführt. Jeder Befehl hat eine Ausführungszeit  $t_{I}$ . Die Ausführungszeit des Programms ergibt sich dann zu:

$$t_{EX} = n_{C} \cdot t_{C} = \frac{n_{I}}{II P} \cdot t_{I}$$

(1.2)

Die Ausführungszeit eines Befehls  $t_I$  ergibt sich aus der Anzahl der Taktzyklen je Befehl CPI und der Taktzykluszeit  $t_C$ :

$$\mathbf{t}_{\mathsf{I}} = \mathsf{CPI} \cdot \mathbf{t}_{\mathsf{C}} \tag{1.3}$$

Damit wird

$$t_{EX} = n_{I} \cdot t_{C} \cdot \frac{CPI}{ILP} = \frac{n_{I} \cdot t_{C}}{IPC}$$

(1.4)

Hieraus ergibt sich die Anzahl der Befehle je Taktzyklus IPC als Verhältnis der Anzahl der ausgeführten Befehle  $n_I$  zur Anzahl der Taktzyklen  $n_C$ :

$$IPC = \frac{n_{l} \cdot t_{C}}{t_{EX}} = \frac{n_{l} \cdot t_{C}}{n_{C} \cdot t_{C}} = \frac{n_{l}}{n_{C}} = t_{C} \cdot \frac{n_{l}}{t_{EX}}$$

(1.5)

Die Ausführungszeit  $t_{EX}$  ist zumeist eine Entwicklungsvorgabe, die sich aus den Realzeitanforderungen ergibt. Aus dem Programm ist ersichtlich, wieviele Befehle auszuführen sind (Anzahl  $n_I$ ). Ist die Taktfrequenz vorgegeben, kann man mit (1.5) ausrechnen, wieviele Befehle je Taktzyklus ausgeführt werden müssen. Kommt man mit einem Einzelprozessor aus oder braucht man eine Superskalarmaschine? IPC>1 bedeutet, dass in jedem Taktzyklus mehrere Befehle auszuführen sind. Aus (1.1) ergibt sich, wieviele das sind:

$$ILP = IPC \cdot CPI \tag{1.6}$$

Ist IPC < 1, kann es sein, dass der Einzelprozessor genügt. Das ist dann der Fall, wenn ILP gemäß (1.6) kleiner als Eins ist.

Ergibt sich ein ILP > 1, ist nachzusehen, ob ein passender Superskalarprozessor verfügbar ist. Wenn der zur Wahl stehende Prozessor die Ausführungszeit  $t_{\rm EX}$  einhalten kann, ist es in Ordnung. Ansonsten könnte ein Ausweg darin bestehen,  $t_{\rm C}$  zu verkürzen, also die Taktfrequenz zu erhöhen. Ist das nicht möglich, könnte man probieren, ob eine andere Prozessorarchitektur besser geeignet ist. Eine weitere Alternative könnte darin bestehen, einen anwendungsspezifischen Prozessor mit genügend vielen Verarbeitungswerken selbst zu entwerfen. In der Praxis dürfte das zumeist auf einen Spezialprozessor hinauslaufen, der mehrere Verarbeitungswerke enthält, aber in seinen Wirkprinzipien nicht allzu kompliziert ist.

# Die Verarbeitungsleistung

Dauert die Ausführung eines Befehls CPI Taktzyklen, werden ILP Befehle gleichzeitig ausgeführt und beträgt die Taktfrequenz  $f_c$  Hz, so ergibt sich die Verarbeitungsleistung  $P_I$  in Befehlen/Sekunde folgendermaßen:

$$IPS = f_c \cdot \frac{ILP}{CPI} = f_C \cdot IPC$$

(1.7)

Die Verarbeitungsleistung kann auch aus der Ausführungszeit  $t_{EX}$  eines Programms und der Anzahl  $n_I$  der ausgeführten Befehle errechnet werden:

$$IPS = \frac{n_l}{t_{EX}}$$

(1.8)

Der herkömmliche Einzelprozessor führt zu einer Zeit jeweils einen Befehl aus, der nur eine einzige Operation anweisen kann. Somit ist ILP = 1 und es gilt

$$IPS = \frac{f_C}{CPI}$$

(1.9)

#### CPI und ILP in der Praxis

Diese Werte als konstant anzusehen ist nur eine grobe Näherung. Der herkömmliche Einzelprozessor benötigt für jeden Befehl mindestens einen Taktzyklus. Es können aber auch mehrere sein. Das hängt von der Befehlswirkung und von verschiedenen Nebenumständen ab (beispielsweise davon, ob sich die zu verarbeitende Daten im Cache befinden oder ob bei Speicherzugriffen Wartezustände auftreten). Das gilt sinngemäß für die Parallelarbeit in Superskalarprozessoren. Typisch sind zwei bis acht Befehle je Taktzyklus. Aber auch dieser Wert ist nicht konstant. Er hängt unter anderem davon ab, welche Befehle aufeinander folgen und auf welche Daten sie zugreifen. Für genauere Rechnungen müssen deshalb Erwartungswerte angesetzt werden.

#### Einfache Prozessoren

Ist der Prozessor einfach, sind die Verhältnisse überschaubar. Man ist bestrebt, in jedem Taktzyklus einen Befehl auszuführen. Die Marketingangabe, die kennzeichnet, dass man dieses Ziel näherungsweise erreicht hat, lautet "1 MIPS pro MHz". Sie drückt nichts anderes aus als den hier in Rede stehenden Sachverhalt (ein Befehl je Taktzyklus), klingt aber viel großartiger...

Diese auf die Taktfrequenz f<sub>C</sub> bezogen Prozessorleistung P<sub>C</sub> ergibt sich wie folgt:

$$P_{C} = \frac{IPS}{f_{C}} = IPS \cdot t_{C} \cdot \frac{1}{MHz}$$

(1.10)

Die in einfachen Prozessoren erreichbaren Befehlsausführungszeiten hängen von der Taktzykluszeit ab, die sich letzten Endes aus der Schaltungstruktur und der Schaltkreistechnologie ergibt. Man kann – den RISC-Grundsätzen (s. weiter unten) gemäß – die Befehlswirkungen auf jene Operationen beschränken, die durch kombinatorische Zuordnung zu erledigen sind. Dann erfordert jeder Befehl nur einen einzigen Taktzyklus. Die Taktfrequenz  $f_C$  in Hz entspricht dann der Verarbeitungsleistung in Befehlen je Sekunde:

$$IPS = \frac{1}{t_c} \cdot 1 \text{ Befehl} = f_c \text{ Befehle/s}$$

(1.11)

Mehr geht nicht. Zur Leistungssteigerung verbleiben zwei Wege:

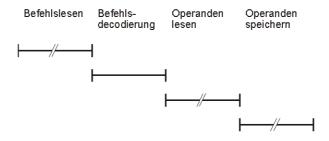

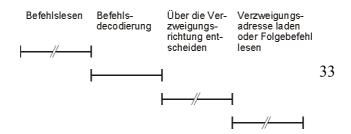

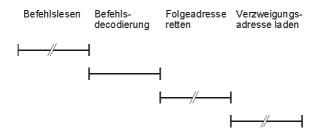

- Befehlspipelining. Das Holen der Befehle, die Befehlsdecodierung usw. wird mit der eigentlichen Operationsausführung überlappt, so dass sich mehrere Befehle in verschiedenen Phasen der Befehlsausführung befinden. Die Taktperiode t<sub>c</sub> ergibt sich dann aus der Verzögerungszeit des Operationswerks.

- Parallelausführung. Es werden auf welche Weise auch immer mehrere Befehle gleichzeitig ausgeführt (Superskalarprinzip).

Diese Maßnahmen wirken aber nicht ständig, sondern nur mit einer gewissen Wahrscheinlichkeit oder Trefferrate. Es ist nicht immer möglich, eine bestimmte Anzahl an Befehlen gleichzeitig auszuführen. Beim Befehlspipelining müssen auch die Speicherschnittstellen mit der kurzen Taktperiode zurecht kommen, sonst gibt es Wartezustände. Die Abhilfe sind Caches, Befehlspuffer usw. Sprungbefehle und Datenabhängigkeiten führen dazu, dass der lückenlose Befehlsstrom zeitweise aufgehalten wird. Je komplexer der Prozessor, desto schwieriger ist es, die Dauer der Befehlsausführung zu bestimmen. Nicht alle Befehle benötigen gleich viele Taktzyklen. Bei einigen Befehle kann sie von den Werten zu verarbeitenden Daten abhängen (z. B. bei der Multiplikation und Division), bei manchen von den Adressen. Die Belegung der Caches, Sprungzielpuffer, Speicherschnittstellen usw. wirkt sich auf die Dauer der Befehlsausführung aus. Im Datenmaterial sind manchmal genauere Angaben zu finden. Da meist nicht bekannt ist, wann welche Betriebszustände vorliegen, kann man sie nur auf Grundlage von Wahrscheinlichkeitsschätzungen auswerten.

## Taktzykluszeit und Schaltungstiefe

Ein Verarbeitungswerk ist ein Schaltnetz, das ein- und ausgangsseitig mit Registern (Flipflops oder Latches) verbunden ist (vgl. Abbildung 2.4). Die minimale Taktzykluszeit  $t_C$ , mit der man eine solche Funktionseinheit betreiben kann, hängt von der Schaltungstiefe s und von Zeitkennwerten ab, die sich aus der Schaltkreistechnologie ergeben:

$$\mathbf{t}_{\mathrm{C}} = \mathbf{s} \cdot \mathbf{t}_{\mathrm{p\_g}} + \mathbf{t}_{\mathrm{p\_d}} + \mathbf{t}_{\mathrm{prop}} + \mathbf{t}_{\mathrm{su}} + \mathbf{t}_{\mathrm{skew}} \tag{1.12}$$

$t_{p\_g}$ : Gatterverzögerungszeit;  $t_{p\_d}$ : Datenverzögerungszeit der Flipflops;  $t_{prop}$ : Signallaufzeit über die Signalwege;  $t_{su}$ : Vorhaltezeit der Flipflops;  $t_{skew}$ : Takttoleranz.

Ist die Schaltkreistechnologie vorgegeben, kann man den Taktzyklus nur kurz halten, indem man die Schaltungstiefe auf den Wert beschränkt, der aus (1.12) berechnet werden kann. Es bleibt dann die Frage, ob man mit sehr geringen Schaltungstiefen auch Verknüpfungen implementieren kann, die anwendungsseitig brauchbar sind. Im Universalprozessor ist es üblicherweise die binäre Addition über die gesamte Verarbeitungsbreite, die die Schaltungstiefe s bestimmt; damit ergibt sich die maximale Taktfrequenz gemäß (1.12) letzten Endes aus dem Zeitbedarf der Addition.

# RISC – die entscheidende Überlegung

Die elementaren Befehle (Laden, Speichern, Addieren, Vergleichen, Verzweigen usw.) werden am häufigsten genutzt. Solche Befehle sind beispielsweise mit einer Schaltungstiefe s = 10 zu implementieren. Damit lässt sich eine entsprechend kurze Zykluszeit t<sub>C</sub> erreichen. Wird durch Hinzufügen komplexerer Befehle die Schaltungstiefe auch nur um 1 erhöht, so werden *alle* Abläufe um 10 % langsamer. Die Nutzungshäufigkeit und Leistungsfähigkeit der hinzugefügten Befehle müsste also so groß sein, dass der Leistungsverlust von 10 % mehr als aufgewogen wird.

Die Ziele der "klassischen" (sprich: akademischen) RISC-Entwicklung:

- Der Prozessor soll in jedem Taktzyklus einen Befehl ausführen können (1 MIPS/MHz). Damit werden nur Befehlswirkungen zugelassen, die mit kombinatorischen Zuordnungen implementiert werden können bestehen.

- Die Befehlswirkungen sollen so einfach sein, dass man den Schaltkreis mit möglichst vielen MHz betreiben kann (einfache Befehlswirkungen einfache Schaltungsstrukturen geringe Schaltungstiefe).

- Alles, was komplizierter ist, soll die Software erledigen (Compiler + Laufzeitsystem).

In der Praxis sieht man es aber nicht so verbissen (Abschnitt 3.7).

#### MIPS und FLOPS

Setzt man die Taktfrequenz in MHz an, so hat die Leistungsangabe IPS die Maßeinheit Millionen Befehle/s oder MIPS (Millions of Instructions per Second). Handelt es sich um Operationen mit Gleitkommazahlen (Floating Point Operations), werden die MIPS zu FLOPS (MFLOPS, wenn Millionen, GFLOPS, wenn Milliarden und TFLOPS, wenn Billionen solcher Operationen in einer Sekunde ausgeführt werden).

### Es sind typische Hausnummern

.. um es vorsichtig auszudrücken<sup>15</sup>. Diese Angaben betreffen nämlich zumeist die lückenlos aufeinanderfolgende Abarbeitung der jeweiligen Befehle unter den jeweils günstigsten Bedingungen. Die gigantischsten Werte stammen von Multiprozessorsystemen, die hunderte, manchmal mehrere tausend Prozessoren enthalten. Die vielen TFLOPS ergeben sich nach folgender Milchmädchenrechnung:

Gesamtleistung des Systems =

Anzahl der Prozessoren • Maximalleistung des einzelnen Prozessors (1.14)

Viele Leistungsangaben beruhen auf dieser einfachen Formel. In der Praxis werden aber nicht selten nur 10 bis 15 % der theoretischen Maximalleistung (Peak Performance) wirksam.

<sup>15:</sup> Eine seit längerem in Fachkreisen verbreitete Interpretation: MIPS = Misinformation to Promote Sales ...

Will man verschiedene Architekturen miteinander vergleichen, so ist zu bedenken, dass Befehle in unterschiedlichen Architekturen Unterschiedliches leisten, selbst dann, wenn sie die gleiche Operation auf gleiche Datentypen anwenden (beispielsweise 32-Bit-Binärzahlen zueinander addieren). Sie können sich in den Adressierungsweisen, in der Anzahl der Register, die im Befehl angesprochen werden können, in der Reaktion auf Bedingungen usw. unterscheiden.

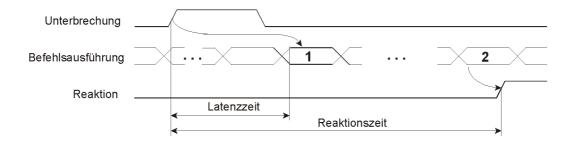

#### Latenz- und Reaktionszeiten

Beide Zeitangaben betreffen Anforderungen, die in der Außenwelt auftreten. Die Latenzzeit (Latency) ist die Zeit zwischen dem Auftreten der Anforderung und dem Beginn der Erledigung. Die Reaktionszeit ist die Zeit zwischen dem Auftreten der Anforderung und der erstenReaktion darauf, die sich in der Außenwelt bemerkbar macht (Abbildung 2.7).

Abb. 2.7 Latenz- und Reaktionszeit am Beispiel einer Unterbrechungsbehandlung. 1 - der erste Befehl der Unterbrechungsbehandlung; 2 - dieser Befehl veranlasst die erste Reaktion in der Außenwelt, beispielsweise das Einschalten einer Leuchtanzeige.

Manche Latenzzeiten sind schaltungstechnisch bedingt und im Datenmaterial des Prozessors angegeben. Das betrifft unter anderem die Zeit zwischen der Unterbrechungsauslösung und dem Beginn der Unterbrechungsbehandlung. Diesen Werten liegen aber immer die günstigsten Betriebsverhältnisse zugrunde (Beispiel: die Unterbrechung ist zugelassen, es sind keine Unterbrechungen höherer Priorität anhängig, der vorhergehende Befehl hat die kürzeste Ausführungszeit, und es gibt keine Wartezustände). In der Praxis sind aber stets die jeweils ungünstigsten Verhältnisse anzusetzen. Und da können aus wenigen hundert Nansosekunden ohne weiteres viele Millisekunden werden... (Beispiel: die Unterbrechung ist zeitweise verhindert, weil im Moment gerade der Betriebssystemkern läuft, es sind noch mehrere Unterbrechungen höherer Priorität anhängig, und das betreffende Programm befindet sich nicht im Arbeitsspeicher.) Das typische Kennzeichen einer guten Realzeitumgebung sind eindeutig voraussehbare Latenz- und Reaktionszeiten. Systemplattformen aus dem Bereich der Personalcomputer können diese Bedingung prinzpbedingt nicht erfüllen, da sie eigentlich für ganz andere Anwendungsgebiete vorgesehen sind, in denen naturgemäß andere Anforderungen erfüllt werden müssen. Präzise vorhersagbare Latenz- und Reaktionszeiten ergeben sich, wenn man alle störenden Einflüsse fernhält (hierzu gehören unter anderem Versuche, auf der selben Maschine weitere Anwendungen laufen zu lassen oder von den Realzeitprogrammen aus direkt aufs Internet zuzugreifen). In letzter Konsequenz führt dies zur Funktionentrennung zwischen Industriestandard- und Realzeitmaschinen, wobei die harten Realzeitaufgaben mit Stand-alone-Programmen oder gar mit selbst entwickelten Schaltungslösungen erledigt werden.

#### Rechnerarchitekturen auswählen

Die heutigen Prozessorarchitekturen kann man als Abmischungen aus vergleichsweise wenigen Grundsatzlösungen ansehen. Wer sich mit einer dieser Architekturen auskennt, wird kaum Schwierigkeiten haben, sich in eine andere einzuarbeiten. Die elementaren Datenstrukturen und

Befehlswirkungen sind im Grunde überall gleich. Die Unterschiede zwischen den Architekturen betreffen vor allem:

- die Wortlänge und Verarbeitungsbreite,

- · das Adressierungsvermögen,

- das Registermodell,

- die Zubringerfunktionen,

- die Speicherorganisation,

- die Speicher- und E-A-Ausstattung.

# **Praxistips zur Architekturauswahl:**

- 1. Die anwendungspraktisch wesentlichen Unterschiede zwischen den einzelnen Architekturen sind viel geringer, als man aufgrund der einschlägigen Werbeaussagen vermuten könnte.

- 2. Die Auslegung der Maschinenbefehle (ob CISC, ob RISC) ist in der Anwendungspraxis nur von geringer Bedeutung.

- 3. Oft kommt es gar nicht auf die Architektur an, sondern auf Kosten, E-A- und Speicherausstattung, Taktfrequenz, Gehäusebauform, Speisespannung und Kompatibilität.

- 4. Alle Architekturen und Befehlssätze sind "powerful" manche mehr, manche weniger...

- 5. Es gibt keine ideale Architektur ja nicht einmal ein allgemeingültiges Optimum. Jede Auslegung ist ein Kompromiss.

- 6. Man gewöhnt sich an alles.

# Rechnerarchitektur und Hochsprachenprogrammierung

Die Programmiersprache sollte eigentlich den Anwendungsprogrammierer von der Maschinenarchitektur unabhängig machen. Wenn das Realzeitraster keine allzu hohen Anforderungen stellt – und somit auf maschinennahe Optimierungen verzichtet werden kann – ist das auch weitgehend der Fall. Beim Auswählen kommt es dann nicht auf Spitzfindigkeiten der Architektur an. Neben den Ausstattungsmerkmalen ist vor allem das pauschale Leistungsvermögen von Bedeutung (damit es schnell genug läuft). Hierzu genügt oft ein kurzer Blick auf Verarbeitungsbreite und Verarbeitungsleistung oder Taktfrequenz, manchmal auch auf den Registersatz. Die ganz grobe Faustregel: Je mehr von all dem, desto besser. Die bessere Faustregel: so viel, dass man nicht von Anfang an zum Tricksen gezwungen ist und dass genügend Reserven für Änderungen und künftige Erweiterungen da sind. Erfahrungsbericht: ausreichende Leistungsreserven ergeben sich von 4 MIPS an aufwärts, bei näherungsweise bei 1 MIPS/MHz also von 4 MHz Taktfrequenz an. Typische nichttriviale Anwendungen, die in Sprachen wie C oder IEC 61131 ST programmiert wurden, laufen dann schnell genug.

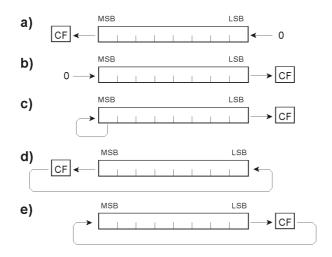

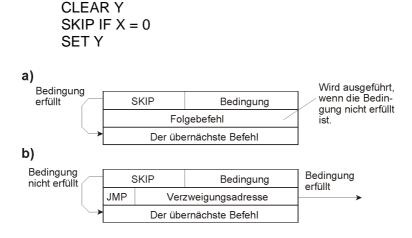

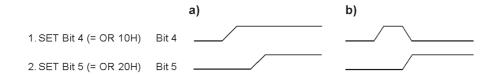

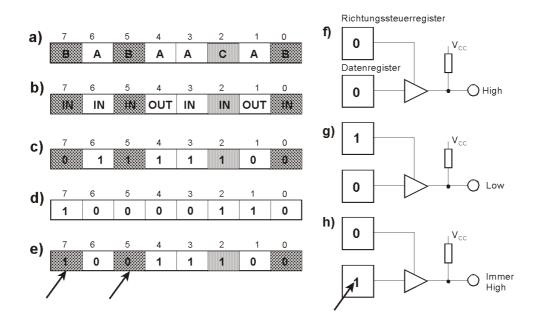

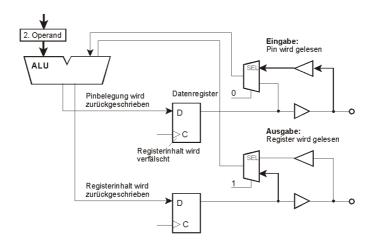

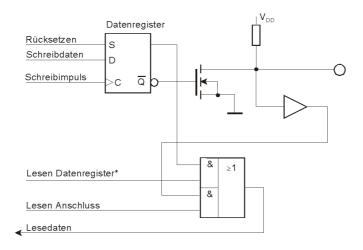

## Rechenmaschinen und Realzeitmaschinen