# ATA I/O Port Adapter 05a / 05ax

# **Programmer's Reference / Hardware Description**

Release: 1.2 vom 19. 9. 06

#### **Purpose:**

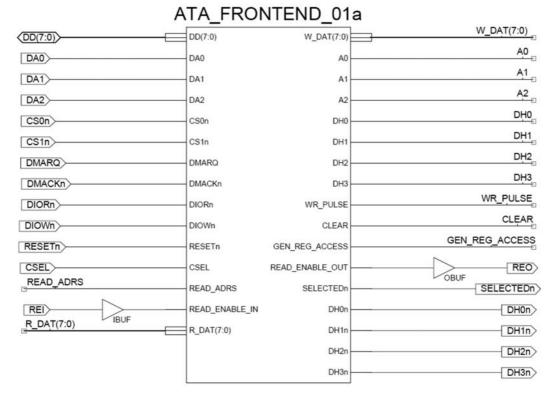

Attachment of five general-purpose I/O ports (8 bits each) to a parallel ATA interface (fig. 1). Under program control, each of the  $5 \cdot 8 = 40$  I/O lines can be used as an input or as an output.

#### ATA I/O port adapter 05a:

Restricted support of selective addressing. This circuit will fit into a Xlinx XC95108 CPLD (package PLCC 84).

#### ATA /O port adapter 05ax:

Complete support of selective addressing. This circuit requires at least a Xilinx XC95144 CPLD (or the like).

Fig. 1 ATA I/O adapter IC comprising five general-purpose I/O ports.

ATA signals supported:

- DD7...0 (8 bit data bus)

- CS0, CS1

- DA2, DA1, DA0

- DIOW, DIORD

- DMARQ, DMACK

- RESET

- CSEL

ATA signals not supported:

- DD15...8

- INTRQ, IORDY

- DASP, PDIAG, CSEL

#### Principles of I/O port operation

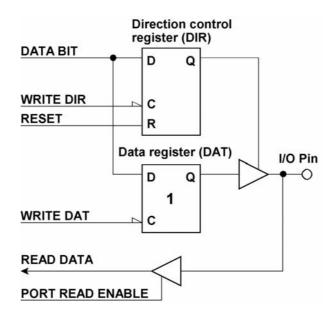

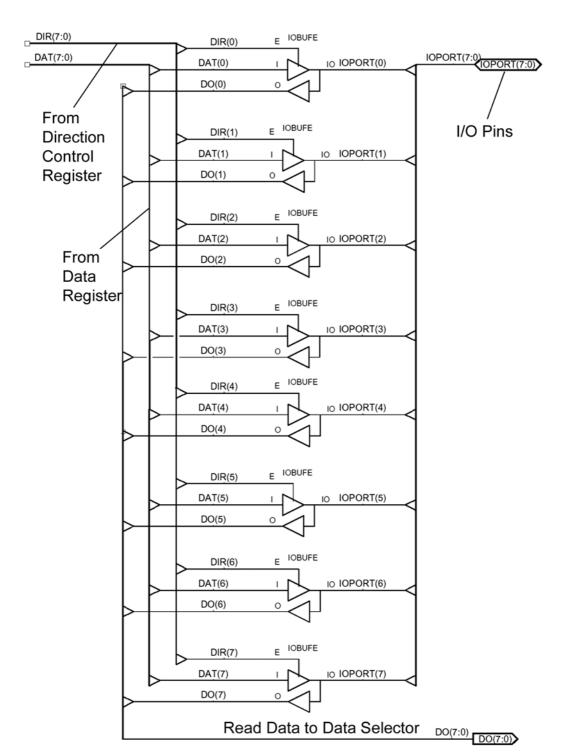

The I/O ports are similar to the typical I/O ports of well-known microcontroller families (Microchip PIC, Atmel AVR and the like). Each I/O port comprises a direction control register (DIR) and a data register (DAT). The DIR bit positions control the direction of the corresponding I/O signals (fig. 2):

- If the DIR bit is set to zero, the corresponding I/O pin is configured as an input, the pin driver being in high impedance state.

- If the DIR bit is set to one, the corresponding I/O pin is configured as an output. The potential (low or high) on the I/O pin corresponds to the bit in the DAT register.

After reset:

DIR = 00H (all I/O pins are in high impedance state), DAT = 00H.

Fig. 2 Principal structure of an I/O bit position.

#### ATA device selection

Via the CSEL input, the I/O adapter can be configured as device 0 (master) or device 1 (slave):

- CSEL = 0: Master (Device 0),

- CSEL = 1: Slave (Device 1).

Typically, CSEL will be wired to Low or High potential or connected to the CSEL line of the ATA interface (Cable Select).

ATA I/O PORT ADAPTER 05A/05A1 F

#### I/O addressing

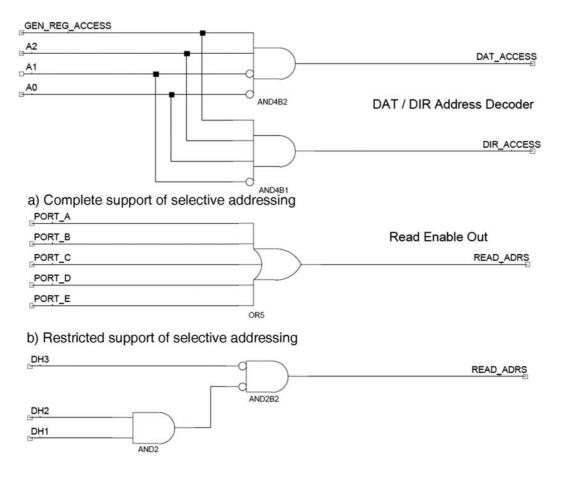

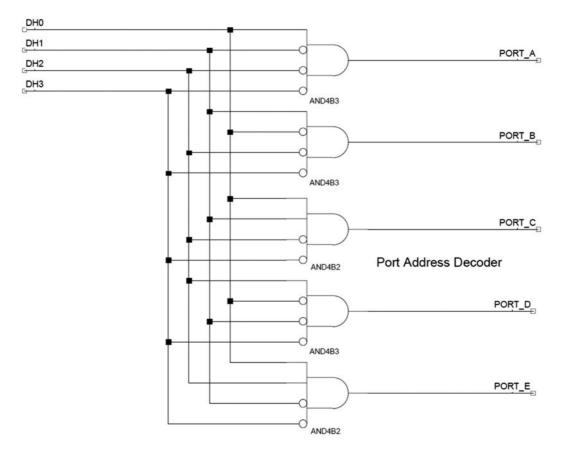

Each of the five ports (A... E) has its own port address in the DH register (fig. 3, table 1). Within each port, the data register (DAT) as well as the direction control register (DIR) are to be addressed (table 2).

| 7 | 6 | 5 | 4      | 3                                 | 2 | 1 | 0  |

|---|---|---|--------|-----------------------------------|---|---|----|

| - | - | - | DEVICE | I/O Port Selection (Port Address) |   |   | s) |

| DH register bits 3 0 | I/O port  |  |  |

|----------------------|-----------|--|--|

| 1H                   | Port A    |  |  |

| 2H                   | Port B    |  |  |

| 3H                   | Port C    |  |  |

| 4H                   | Port D    |  |  |

| 5H                   | Port E    |  |  |

| all other values     | no effect |  |  |

| Fig. 3 | DH register content. |

|--------|----------------------|

|--------|----------------------|

Table 1 I/O Port addressing via DH register.

| C  | S  | Reg | ister | Addre | ss DA |                                                 | Legacy ATA Ports |     |     |     |

|----|----|-----|-------|-------|-------|-------------------------------------------------|------------------|-----|-----|-----|

| 1- | 0- | 2   | 1     | 0     | Hex   | Register                                        | 1                | 2   | 3   | 4   |

| 1  | 0  | 1   | 0     | 0     | 4     | Data register (DAT)                             | 1F4              | 174 | 1EC | 16C |

| 1  | 0  | 1   | 0     | 1     | 5     | Direction control register (DIR)                | 1F5              | 175 | 1ED | 16D |

| 1  | 0  | 1   | 1     | 0     | 6     | Device selection and port address register (DH) | 1F6              | 176 | 1EE | 16  |

*Table 2* Register addressing within a selected I/O port. Read accesses to either DAT or DIR addresses will read back the potentials on the I/O pins.

#### *I/O port selection*

Writing into a register of or reading from an I/O port requires two steps:

- 1. Select the ATA device and the I/O port by writing into the DH register.

- 2. Write to or read from either the data register or the direction control register of the selected port.

A port address loaded into the DH register will be retained. Therefore, if an already selected port is to be accessed, step 1 could be skipped.

#### Write operations

A write access to one of the ATA port addresses according to table 2 will write the data byte into the DH register or into the data register or the direction control register of the selected I/O port. A write access with any other address has no effect upon the I/O adapter.

ATA I/O PORT ADAPTER 05A/05A1

#### Read operations

Contrary to the operation of some microcontroller ports (like those of the Atmel AVR controllers), only the potentials (low or high) on the I/O pins can be read back. A read access to the direction control register or to the data register will return the potentials on the corresponding I/O pins. If a read access is directed to the DH register or to a port address which does not belong to the allocated range of addresses (selective addressing), the adapter will not act upon the data bus. Thus, the ATA host adapter will deliver a value FFH. The result of read operations with other addresses is not defined.

Writing into a register of an I/O port requires two steps:

- 1. Select the ATA device and the I/O port by writing into the DH register.

- 2. Perform a read access to either the data register or the direction control register of the selected port.

A port address loaded into the DH register will be retained. Therefore, if an already selected port is to be accessed, step 1 could be skipped.

#### Selective addressing

Selective addressing is a provision to permit attaching more than one ATA I/O adapter at one interface cable. With this feature implemented, the adapter will only react on particular port addresses.

- The ATA I/O port adapter 05ax will react only on the port addresses shown in table 1 (1H...5H).

- The ATA I/O port adapter 05a1 will react only on port addresses 0H...5H.

#### Notes:

- 1. The selective addressing feature can be omitted if the adapter will be the only ATA I/O circuit at the interface cable.

- 2. If selective addressing is not to be implemented at all, the READ\_ADRS input of the ATA I/O front end is to be connected to High potential.

#### Diagnostic indications:

These signals are provided to drive LEDs (active low). The LEDs will show:

- Whether the adapter has been selected.

- The port address field of the DH Register (DH3...0).

# ATA I/O port adapter 05a pinout:

| nin | Gianol         | Din 1 | 7 i       |

|-----|----------------|-------|-----------|

|     | Signal<br>Name |       | Signal    |

|     | DD<4>          |       | Name      |

|     |                |       | DH3n      |

|     | PORTE<0>       | 525   | DAO       |

|     | PORTE<1>       |       | DD<0>     |

|     | PORTB<0>       |       | DD<5>     |

|     | PORTB<1>       |       | PORTA<7>  |

|     | PORTA<0>       |       | PORTD<5>  |

|     | PORTD<0>       | 49    |           |

| 8   |                |       | PORTD<7>  |

| 9   | DIOWn          |       | PORTC<5>  |

|     | DIORn          |       | PORTC<7>  |

|     | PORTC<0>       |       | SELECTEDn |

|     | PGND           |       | CSOn      |

|     | DHOn           |       | DMARQ     |

|     | DD<1>          | 56    |           |

|     | PORTE<4>       |       | REO       |

|     | GND            | 58    | 2         |

|     | PORTE<5>       |       | TDO       |

|     | PORTB<4>       | 60    |           |

|     | PORTB<5>       |       | PORTE<6>  |

|     | PORTA<4>       |       | PORTE<7>  |

|     | PORTD<4>       |       | PORTB<6>  |

|     | VCC            |       | VCC       |

|     | PORTC<4>       |       | PORTB<7>  |

|     | DD<7>          |       | PORTA<6>  |

|     | PGND           |       | PORTD<6>  |

|     | DA2            | 68    | PORTC<6>  |

|     | GND            |       | CS1n      |

|     | TDI            |       | DA1       |

|     | TMS            | 71    | DD<3>     |

| 30  | TCK            |       | PORTE<2>  |

| 31  | CSEL           | 73    | VCC       |

| 32  | DD<6>          | 74    | RESETn    |

| 33  | PORTA<1>       | 75    | PORTE<3>  |

| 34  | PORTA<3>       | 76    | REI       |

| 35  | PORTA<5>       | 77    | PGND      |

| 36  | PORTD<1>       | 78    | VCC       |

| 37  | PORTD<3>       | 79    | PORTB<2>  |

|     | VCC            | 80    | PORTB<3>  |

|     | PORTC<1>       | 81    | porta<2>  |

| 40  | PORTC<3>       | 82    | PORTD<2>  |

| 41  | DH1n           | 83    | PORTC<2>  |

| 42  | GND            | 84    | DH2n      |

|     |                |       |           |

| 45<br>14<br>58<br>71<br>1<br>46<br>32<br>24                                                                               | DD0<br>DD1<br>DD2<br>DD3<br>DD4<br>DD5<br>DD6<br>DD7                                    | A05a A0<br>A1<br>A2<br>A3<br>A4<br>A5<br>A6<br>A7                                                               | 6           33           81           34           20           35           66           47                                                                                               |

|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 44<br>70<br>26<br>54<br>69<br>10<br>9<br>55<br>56<br>31                                                                   | DA0<br>DA1<br>DA2<br>CS0n<br>CS1n<br>DIORn<br>DIOWn<br>DIOWn<br>DMARQ<br>DMACKn<br>CSEL | B0<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6<br>B7<br>C0<br>C1<br>C2<br>C3<br>C4<br>C5                                | 4         5         79         80         18         19         63         65         11         39         83         40         23         51         68                                 |

| $ \begin{array}{r} 74 \\ 22 \\ 38 \\ 64 \\ 73 \\ 78 \\ 8 \\ 12 \\ 16 \\ 25 \\ 27 \\ 42 \\ 49 \\ 60 \\ 77 \\ \end{array} $ | RESETn<br>V <sub>cc</sub><br>GND                                                        | C6<br>C7<br>D0<br>D1<br>D2<br>D3<br>D4<br>D5<br>D6<br>D7<br>E0<br>E1<br>E2<br>E3<br>E4<br>E5<br>E6<br>E7<br>RE0 | 52         7         36         82         37         21         48         67         50         2         3         72         75         15         17         61         62         57 |

| 76<br>28<br>30                                                                                                            | REI<br>TDI<br>TMS<br>TCK                                                                | SELECTEDn<br>DH0n<br>DH1n<br>DH2n<br>DH3n<br>TDO                                                                | 53         13         41         84         43         59                                                                                                                                  |

### The ATA interface:

### DAT / DIR address decoder and selective addressing:

### Port address decoder:

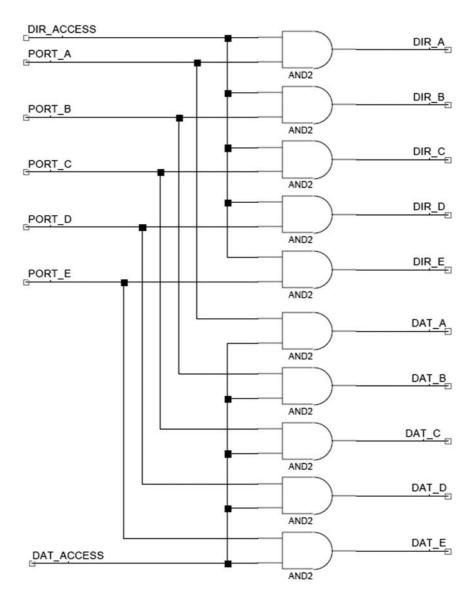

# Write enable signals to all of the DIR and DAT registers:

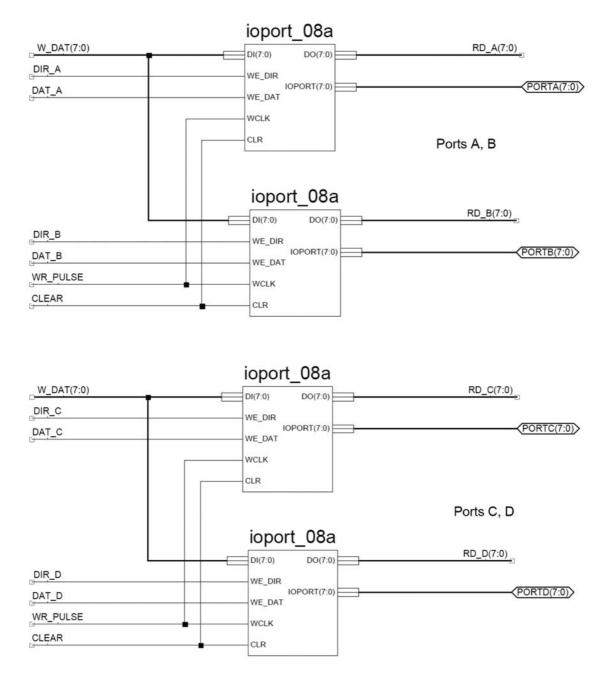

# I/O ports A to D:

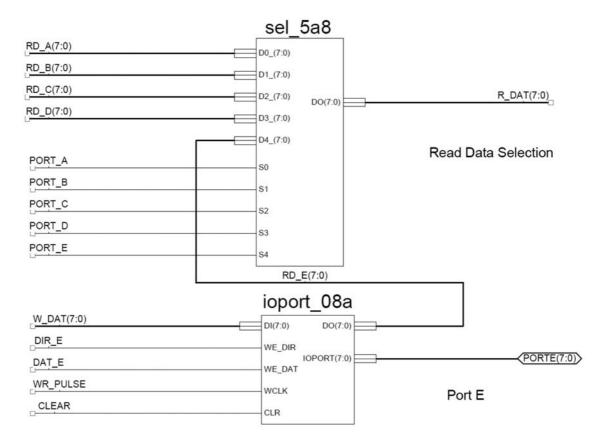

### Read data selector and I/O port E:

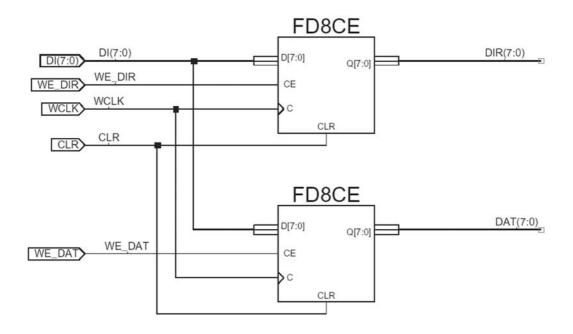

## Internals of an I/O port (1): DIR and DAT registers:

# Internals of an I/O port (2): Drivers, buffers, and I/O pins: