# 7. Parallele Schnittstelle

# 7.1. Grundlagen

Die parallele Schnittstelle ist ein E-A-Interface mit 8-Bit-Datenbus und asynchroner Datenübertragung, die durch Handshake-Signale gesteuert wird. Zusätzlich sind Leitungen vorgesehen, um Sonder- und Fehlerbedingungen vom angeschlossenen Gerät an den PC zurückzumelden.

#### Zweckbestimmung

Die parallele Schnittstelle war ursprünglich als reines Ausgabe-Interface zum Anschließen von Druckern vorgesehen (Centronics-Schnittstelle). Im Laufe der Zeit wurde die Schnittstelle als Einfachinterface zum Anschließen vielfältiger Geräte ausgenutzt (Scanner, Videokameras, Datensicherungslaufwerke usw.). Des weiteren dient sie dazu, zwei PCs zwecks Datenaustausch miteinander zu koppeln (PC-Direktverbindung).

## Die herkömmmliche Parallelschnittstelle (Centronics-Schnittstelle)

Das Interface wurde in den 70er Jahren als kostengünstige Druckerschnittstelle für die Nahaufstellung (wenige Meter Kabellänge) entwickelt. Kennzeichnende Merkmale:

- 8-Bit-Bus zur Datenausgabe,

- asynchrone Steuerung der Datenübertrragung über Handshake-Signale,

- zusätzliche Signale zur Druckersteuerung (Initialisierung, Zeilenvorschub) und zur Rückmeldung typischer Fehlerzustände (kein Papier, allgemeiner Druckerfehler),

- TTL-Signalpegel,

- Nutzung üblicher TTL-Schaltkresie als Treiber und Empfänger,

- ein spezieller 36-poliger Steckverbinder (Centronics-Steckverbinder).

## Die Parallelschnittstelle im PC

Es handelt sich um eine Einfachsteuerung. Die Hardware besteht im Grunde nur aus 3 programmseitig zugänglichen Registern, an die die Interfaceleitungen angeschlossen sind. Somit kann man die auswärtsführenden Leitungen programmseitig einstellen und die einwärtsführenden abfragen. Zudem kann das vom Drucker kommende Bestätigungssignal einen Interrupt auslösen. Alle Funktionen sind mit Software zu realisieren; es gibt keine Ablaufsteuerschaltungen, State Machines o. dergl.

## Die Parallelschnittstelle des PS/2 (Extended Printer Port EPT)

Die Einfachlösung (3 Register, reine Programmsteuerung) wurde beibehalten. Es wurden aber die 8 Datenleitungen bidirektional ausgelegt, so daß das Interface auch für die byteparallele Eingabe genutzt werden kann. Umschaltung zwischen Ein- und Ausgabe: über ein Steuerbit in einem der Register.

#### **Der Standard IEEE 1284**

Dieser Standard (1994 eingeführt) definiert byteparallele bidirektionale Hochgeschwindigkeits-Schnittstellen (50...100 mal schneller als das herkömmliche Centronics-Interface). Es sind insgesamt 5 Betriebsarten vorgesehen:

- Standard Printer Port (SPP). Die herkömmliche Parallelschnittstelle. Auch: Compatibility-Modus.

- Nibble-Modus. Betrieb der herkömmlichen Parallelschnittstelle in einem 4-Bit-Eingabemodus. Zum Abholen der Konfigurationsdaten (des Gerätes) und zum "Aushandeln" der eigentlichen Betriebsweise.

- Byte-Modus. Der Extended Printer Port des PS/2.

- EPP (Enhanced Printer Port),

- ECP (Enhanced Capability Port).

EPP und ECP sind Hochgeschwindigkeits-Schnittstellen. Die hohen Datenraten werden durch hardwareseitige (autonome) Steuerung der Signalspiele erreicht. Zudem sind im Standard auch die elektrischen Kennwerte und das Kabelmaterial entsprechend angemessen spezifiziert.

## Die Parallelschnittstelle in modernen PCs

Sie gilt als sog. Legacy Device, also als Erblast aus der Vergangenheit (so sehen es zumindest Intel und Microsoft). Besonders fortschrittliche PCs haben gar keine mehr. Ist eine solche Schnittstelle vorhanden, so befindet sich die betreffende Hardware in einem Super-IO-Schaltkreis.

#### Welche Betriebsarten werden unterstützt?

Alle modernen Schaltkreise entsprechen IEEE 1284. Es ist aber mit kleinen Unterschieden zu rechnen. Zudem kommt es darauf an, wie das BIOS die Vorkehrungen des Schaltkreises ausnutzt (es werden nicht immer alle eingebauten Funktionen unterstützt). So fehlt manchmal die Unterstützung des Byte Mode (= des bidirektionalen PS/2-Printerports), Was unbedingt funktionieren muß: Compatibility-Modus (Standard Printer Port SPP) und Nibble-Modus. Microsoft empfiehlt (seit Windows 95) zudem den ECP-Modus.

## Betriebsarteneinstellung

Typischerweise übers BIOS-Setup. *Praxistip:* Dort nachsehen, was sich einstellen läßt (so erkennt man, welche Betriebsarten im betreffenden Computer tatsächlich unterstützt werden). Die jeweils benötigte Betriebsart sollte im Setup ausgewählt werden, so daß sie schon beim Hochfahren eingerichtet werden kann. Es gibt aber Treiber-und Dienstsoftware (liegt oft entsprechenden Geräten bei), die es ermöglicht, auch während der Nutzung des Systems die Betriebsart zu wechseln. *Achtung:* Solche Programme kommen manchmal nur mit bestimmten Super-IO-Typen zurecht. Wenn es nicht funktioniert: nach Updates und anderen/neueren Versionen umsehen (Internet; Einstieg über die Web-Sites der Gerätehersteller).

## Parallelschnittstellen über den USB betreiben

Der USB ermöglicht es, parallele Schnittstellen über Interfacewandler zu betreiben. USB ist aber (ander als z. B. Serial ATA) keineswegs ein transparentes Protokoll, das "einfach" Registerinhalte und Signalbelegungen über serielle Wege transportiert. Deshalb werden Registerzugriffe auf die herkömmlichen Portadressen nicht unterstützt. Der einzige Zugang führt über die Anwendungsprogrammschnittstellen der jeweiligen Systemplattform (z. B. Windows oder Linux). Über den USB angeschlossene parallele Schnittstellen können somit nur von Programmen genutzt werden, die sich an die betreffenden Systemkonventionen halten; Programme, die herkömmliche Schnittstellen über direkte Registerzugriffe ansteuern, werden nicht funktionieren.

## 7.2. Steckverbinder und Kabel

## Anschlüsse an PCs und Geräten

Die Schnittstelle am PC hat einen 25-poligen "weiblichen" D-Sub-Steckverbinder (Buchsen). Anordnung:

- in einem Slot-Abdeckblech oder im Gehäuse. Verbindung mit dem Motherboard über Flachbandkabel und 26-poligen Pfostensteckverbinder.

- im Slot-Abdeckblech einer entsprechende Steckkarte,

- im E-A-Anschlußblock (Motherboards in ATX-Formfaktoren).

#### Herkömmliche Geräteanschlüssse:

- Drucker: Centronis, 36-polig, "weiblich",

- andere Geräte (z. B. Scanner): D-Sub, 25-polig, "männlich" (Stifte).

## Das typische Druckerkabel

Es hat einerseits einen "männlichen" 25-poligen D-Sub-Steckverbinder und andererseits einen "männlichen" 36-poligen Centronics-Steckverbinder.

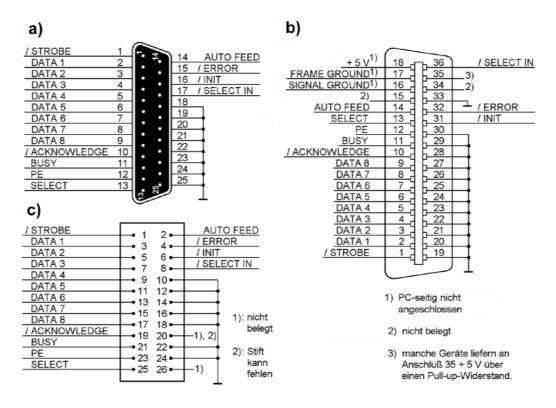

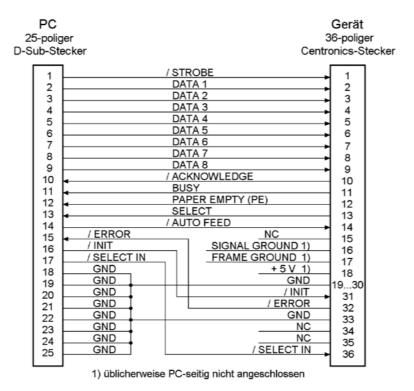

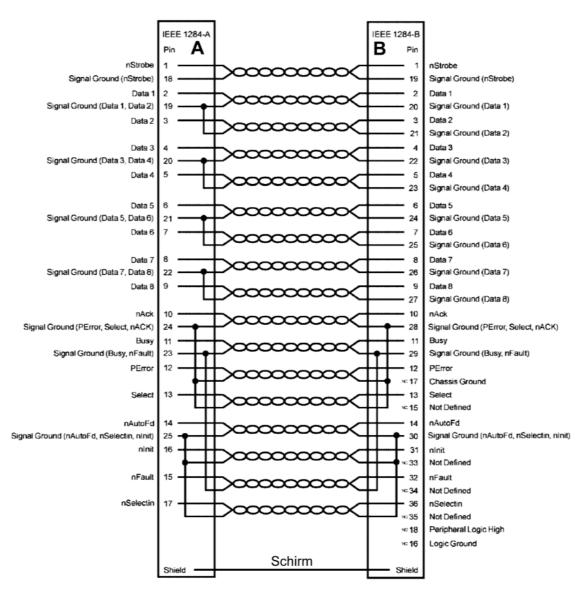

Abbildung 7.1 zeigt die Belegung der verschiedenen Steckverbinder (jeweils mit Blick auf die Steckseite). Abbildung 7.2 veranschaulicht den Aufbau eines herkömmlichen Druckerkabels (und damit auch die Anschlußbelegung beider Seiten).

## Anschlußkabel für Scanner usw.

Sie haben zwei 25-polige D-Sub-Steckverbinder, und zwar einen "männlichen" und einen "weiblichen" (also Stifte einerseits und Buchsen andereseits). Verbindungssschema: 1:1.

#### Achtung:

Manchmal kommt es darauf an. 1:1-Kabel mit 25-poligen D-Sub-Steckverbindern gibt es auch für die serielle Schnittstelle. Sie entsprechen aber in Kabelmaterial, Verdrillung und Masseverbindungen in keiner Weise dem Standard IEEE 1284 (vgl. weiter unten Tabelle 7.1).

**Abbildung 7.1** Steckverbinder der Parallelschnittstelle. a) Interfacestecker, PC-seitig; b) Stecker am Kabel, geräteseitig; c) Pfostenstecker auf Motherboard (zum Anschließen von D-Sub-Steckerrn über Flachbandkabel)

Abbildung 7.2 Centronics-Interfacekabel für IBM-kompatible PCs

## Die + 5 V am geräteseitigen Steckverbinder

Die Spannung wird vom angeschlossenen Gerät geliefert. Sie ist typischerweise mit ca. 80 mA belastbar. Anwendung: vor allem für vorzuschaltende Puffer (Centronics Booster) und Interfacewandler (z. B. seriell auf parallel). Der PC bekommt diese Spannung gar nicht zu sehen. Des weiteren liefern manche Geräte an Anschluß 35 + 5 V über einen Pull-Up-Widerstand. Der Zweck: für bestimmte Sonderverkabelungen einen festen High-Pegel bereitzustellen. Sie sollten sich aber nicht 100%ig darauf verlassen!

#### Kabellänge

Die Kabellänge ist auf etwa 2...3 m begrenzt; manchmal werden aber auch noch Installationen mit 5...7 m ordnungsgemäß arbeiten. Um größere Entfernungen zu überbrücken, gibt es entsprechende Puffer (Booster) bzw. Interfacewandler.

### Achtung:

Die herkömmliche Schnittstelle ist elektrisch nicht besonders robust. Kabel nur ziehen oder stecken, wenn PC und Gerät ausgeschaltet sind! IEEE 1284 hält hingegen Hot Plugging aus.

#### Kahelmaterial

Damit steht es nicht immer zum besten. Die Mängel mancher handelsüblichen Druckerkabel: keine oder unzureichende Verdrillung, zu dünner Draht, inkorrekte Abschirmung.

## Praxistips:

- 1. Verdrillung. Strenggenommen brauchen wir paarweise verdrilltes, geschirmtes Kabel (Shielded Twisted Pair STP) mit 17 Adernpaaren, wobei zu jeder Signalleitung eine mit ihr verdrillte Masseleitung vorgesehen wird.

- 2. Wellenwiderstand: 60...150 Ohm.

- 3. Draht: Litze 28...24 AWG (bzw. wenigstens 0,08 mm²). Derartiges Kabel ist allerdings recht teuer und auch ziemlich dick und steif (z. B. hat ein Kabel mit 24 AWG Adernpaaren einen Außendurchmesser von etwa 12 mm).

- 4. Zu Prüfzwecken ein wirklich hochwertiges Kabel von etwa 3 m Länge bereithalten (ist handelsüblich, aber das Selbstkonfektionieren gibt Gelegenheit, einige Fertigkeiten zu üben). Wenn es damit funktioniert, wissen Sie, daß es sich lohnt, auch für die konkrete PC-Installation ein passendes Kabel zu kaufen oder anzufertigen.

#### Steckverbinder und Kabel nach IEEE 1284

Im Standard werden 3 Steckverbindertypen spezifiziert:

- der herkömmliche 25-polige D-Sub-Steckverbinder (1284-A),

- der herkömmliche 36-polige Centronics-Steckverbinder (1284-B),

- ein neuer 36-poliger miniaturisierter Centronics-Steckverbinder (1284-C).

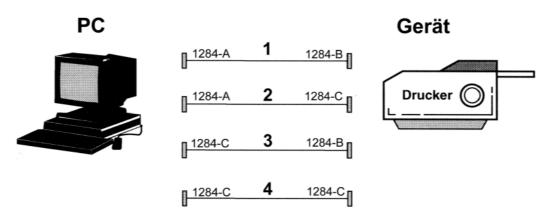

Damit ergeben sich verschiedene Arten der Verkabelung (Abbildung 7.3). Im Standard wird die Ausstattung mit Steckverbindern 1284-C empfohlen. Viele Geräte (vor allem Drucker) werden aber nach wie vor mit den großen Centronics-Steckverbindern (1284-B) bestückt.

Abbildung 7.3 Verbindungen zwischen PC und peripherem Gerät nach IEEE 1284

## Erklärung:

1 - herkömmliches Interface; 2 - neues Gerät an herkömmlichem PC; 3 - herkömmliches Gerät an neuem PC; 4 - neues Gerät an neuem PC.

## Hinweis:

Das ist eine idealisierte Darstellung. Offensichtlich haben die Hersteller seit dem Aufkommen des USB an den herkömmlichen Schnittstellen nicht mehr viel getan - das typische Druckerkabel hat auch im 21. Jahrhundert einen 25-poligen D-Sub- und einen herkömmlichen 36-poligen Centronics-Steckverbinder (1284-A + 1284-B).

## Anschlußbelegungen und Kabelaufbau

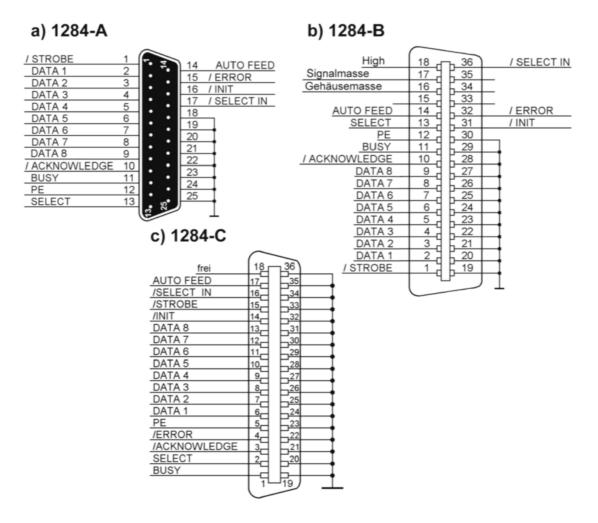

Abbildung 7.4 zeigt die Belegung der Steckverbinder. Aus Tabelle 7.1 ist ersichtlich, wie die Signal- und Masseanschlüsse im einzelnen belegt sind (paarweise verdrillte Adern). Abbildung 7.5 veranschaulicht den Aufbau des nach wie vor wichtigsten Gerätekabels (1284-A auf 1284-B).

| Ci             | 128    | 4-A   | 128    | 84-B  | 1284-C |       |

|----------------|--------|-------|--------|-------|--------|-------|

| Signal         | Signal | Masse | Signal | Masse | Signal | Masse |

| DATA 1         | 2      | 19    | 2      | 20    | 6      | 24    |

| DATA 2         | 3      | 19    | 3      | 21    | 7      | 25    |

| DATA 3         | 4      | 20    | 4      | 22    | 8      | 26    |

| DATA 4         | 5      | 20    | 5      | 23    | 9      | 27    |

| DATA 5         | 6      | 21    | 6      | 24    | 10     | 28    |

| DATA 6         | 7      | 21    | 7      | 25    | 11     | 29    |

| DATA 7         | 8      | 22    | 8      | 26    | 12     | 30    |

| DATA 8         | 9      | 22    | 9      | 27    | 13     | 31    |

| /STROBE        | 1      | 18    | 1      | 19    | 15     | 33    |

| /ACKNOWLEDGE   | 10     | 24    | 10     | 28    | 3      | 21    |

| BUSY           | 11     | 23    | 11     | 28    | 1      | 19    |

| PE             | 12     | 24    | 12     | 29    | 5      | 23    |

| SELECT         | 13     | 24    | 13     | 29    | 2      | 20    |

| /AUTO FEED     | 14     | 25    | 14     | 30    | 17     | 35    |

| /ERROR (FAULT) | 15     | 23    | 32     | 33    | 4      | 22    |

| /INIT          | 16     | 25    | 31     | 30    | 14     | 32    |

| /SELECT IN     | 17     | 25    | 36     | 33    | 16     | 34    |

Tabelle 7.1 Anschlußbelegung der Steckverbinder nach IEEE 1284

Abbildung 7.4 Anschlußbelegung des miniaturisierten Centronics-Steckverbinders (1284-C)

## Kabellänge

Das Interface ist bis zu 10...12 m Kabellänge noch betriebssicher\*). Auf Grund des Handshaking-Signalspiels führen längere Kabel zur Verminderung der Datenrate. Bei 10 m sind noch einige hundert kBytes/s erreichbar, bei etwa 5 m um 2 MBytes. Die höchste Datenrate (10 MBytes/s) erfordert eine Kabellänge von unter 2 m.

\*): Voraussetzung: keine Störeinstrahlung, keine Erdschleifenprobleme (vgl. Kapitel 8). Sind die verbundenen Einrichtungen in einer üblichen Büroumgebung an den gleichen Stromkreisverteiler angeschlossen, gibt es typischerweise kaum Schwierigkeiten.

Abbildung 7.5 Der Aufbau eines üblichen Druckerkabels gemäß IEEE 1284 (nach: IEEE)

## Hinweise:

- 1. 10 MBytes/s bedeutet, daß je Byte 100 ns zur Verfügung stehen. Paarweise verdrilltes Kabel hat einen Verkürzungsfaktor von etwa 0,6. Kabellaufzeit: rund 5 ns/m. In jedes Handshaking-Signalspiel (EPP, ECP) sind 4 Kabellaufzeiten einzurechnen. Die maximale Kabellaufzeit gemäß IEE 1284: 58 ns (entspricht rund 10 m Kabellänge).

- 2. 10 MBytes/s sind nur mit speziellen PCI-Schnittstellenkarten erreichbar. Leistungsgrenzen von Schnittstellen am ISA-Bus, X-Bus oder LPC: etwa 1...2 MBytes/s.

#### Kabelmaterial

Es ist paarweise verdrilltes, geschirmtes Kabel erforderlich, das u. a. folgenden Anforderungen genügen muß:

- 18 Adernpaare,

- Leiterquerschnitt mindestens 28 AWG = 0,08 mm<sup>2</sup>,

- Wellenwiderstand: 62 Ohm,

- Verdrillungsgrad: wenigstens 36 Verdrillungen/m (1 Verdrillung auf 2,5...3 cm).

Ein solches Kabel sollte entsprechend gekennzeichnet sein (IEEE Std 1284-19XX compliant).

# 7.3. Signale und Signalfolgen

# 7.3.1. Signalkennwerte

#### Signalpegel der herkömmlichen Parallelschnittstelle

Das Interface ist TTL-kompatibel:

## Signalpegel gemäß IEEE 1284

Es gibt zwei Spezifikationen:

- IEEE 1284-I schreibt den Stand der Technik fest (TTL-kompatible Pegel, Open-Collector-Treiber). Treiberstrom wenigstens 14 mA, Stromabgabe des Empfängers höchstens 12 mA (bei Low), Stromaufnahme höchstens 0,32 mA (bei High). Signalanstiegszeit (Anhaltswert): höchstens 120 ns zwischen 0,8 und 2 V (bei 2 m Kabellänge).

- IEEE 1284-II fordert: (1) Gegentakt-Treiberstufen (Totem Pole), (2) TTL-Pegel, (3) Treiberstrom wenigstens 14 mA. Stromaufnahme/-abgabe des Empfängers höchstens 20 μA. Anstiegsgeschwindigkeit 0,05...0,4 V/ns (2 V in 5... 40 ns).

# 7.3.2. Treiber und Empfänger

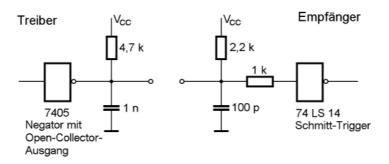

#### Herkömmliche Treiber und Empfänger

Es werden Open-Collector-Treiber verwendet. Die Empfänger sind TTL-Schmitt-Trigger. Im Sinne der Störsicherheit werden die Signalflanken üblicherweise durch eine Zusatzbeschaltung mit Kondensatoren und Widerständen "verschliffen". Abbildung 7.6 zeigt ein Beispiel.

**Abbildung 7.6** Koppelstufen (Treiber, Empfänger) des Centronics-Interfaces (Ausführungsbeispiel; nach: NEC)

#### Hinweise:

- 1. Anstiegszeiten im Bereich mehrerer μs sind nicht immer Fehleranzeichen.

- 2. Schmitt-Trigger keineswegs durch gewöhnliche Negatoren ersetzen.

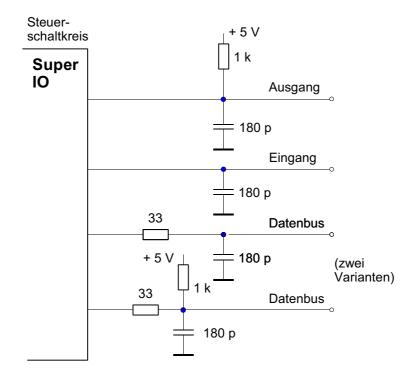

## Schnittstellen nach IEEE 1284

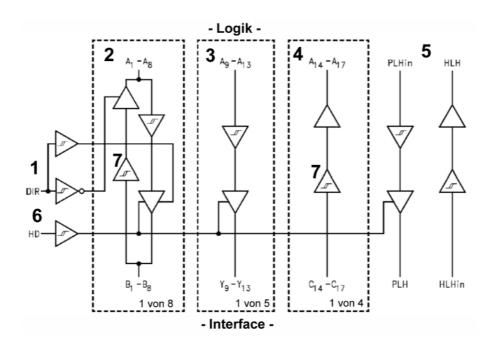

Die Koppelstufen sind direkt in den Super-IO-Schaltkreisen untergebracht. Im PC finden wir deshalb keine besonderen Koppelschaltkreise, sondern lediglich eine Zusatzbeschaltung mit Widerständen und Kondensatoren (Abbildung 7.7). Für die Bestückung von Geräten gibt es eigens Schaltkreise, die alle Treiber und Empfänger der Schnittstelle enthalten (Typenbezeichnung xx161284; Abbildung 7.8).

**Abbildung 7.7** Beschaltung der Schnittstellensignale auf einem Motherboard (nach: Intel/Microsoft). Prinzipdarstellung

Technik der Personalcomputer Technisches Lehrheft 07 Seite 11

**Abbildung 7.8** Ein Koppelschaltkreis (Transceiver) der Typenreihe 161284 (nach: Fairchild Semiconductor)

## Erklärung:

1 - Richtungssteuerung; 2 - bidirektionale Koppelstufen für Datenbus; 3 - Treiberstufen; 4 - Empfängerstufen; 5 - zusätzliche Koppelstufen; 6 - Treiberstufenumschaltung (Open Drain oder Gegentaktausgänge). Treibfähigkeit: 14 mA. 7 - Empfänger mit Schmitt-Trigger-Verhalten. Die Steuersignaleingänge (Position 4) haben eine garantierte Hysterese von 800 mV.

# 7.3.3. Die Signale der herkömmlichen Schnittstelle

## DATA7...0 (8...1)

Die 8 Datensignale sind aktiv High. Ihre Gültigkeit wird durch den STROBE-Impuls bestimmt. Die Daten müssen vor Aktivierung von STROBE stabil anliegen und über die gesamte Aktivierung von STROBE hinweg stabil bleiben. Die Datenbelegung darf sich erst nach dem Inaktivwerden von STROBE ändern.

Zur Numerierung der Bits:

- im PC oder Gerät (Schaltpläne, Registerbelegungen, Programmierhandbücher): meist 7...0,

- an den Steckern: meist 8...1 (Centronics/IEEE 1284).

## /STROBE

STROBE ist aktiv Low, führt vom PC zum Gerät und definiert die Gültigkeit der Datensignale.

## /ACKNOWLEDGE

ACKNOWLEDGE (ACKNLG, ACKN) ist aktiv Low und führt vom Gerät zum PC. Ein ACKNOWLEDGE-Impuls signalisiert das Ende des aktuellen Datenübertragungszyklus.

#### **BUSY**

BUSY ist aktiv High und führt vom Gerät zum PC. Solange BUSY aktiv ist, kann das Gerät keine weiteren Daten über das Interface empfangen. BUSY wird in folgenden Fällen erregt: (1) nach dem Empfang eines jeden Datenbytes, (2) wenn das Gerät zeitweilig nicht in der Lage ist, Daten anzunehmen (Puffer voll), (3) bei einem Gerätefehler, (4) wenn das Gerät grundsätzlich nicht bereit ist (Zustand Off Line).

#### PAPER EMPTY (PE)

PE ist aktiv High, führt vom Gerät zum PC und zeigt an, daß ein manueller Eingriff erforderlich ist. Die typische Nutzung beim Drucker: die Anzeige, daß das Papier ausgegangen ist (Papierendemeldung).

#### Hinweise:

- 1. Bei "Papierende" werden die meisten Drucker "nicht bereit" bzw. "off line", so daß nach dem Einlegen neuen Papiers ggf. die entsprechende Taste (SELECT, ON LINE o. ä.) zu betätigen ist.

- 2. Viele Drucker melden auch Störungen im Papiertransport (z. B. Papierstau) über PE.

#### **SELECT**

SELECT (SLCT) ist aktiv High, führt vom Gerät zum PC und zeigt an, daß das Gerät ausgewählt (also betriebsbereit) ist.

## /AUTO FEED

AUTO FEED ist aktiv Low und führt vom PC zum Gerät. Anwendung beim Drucker: Solange AUTO FEED aktiv ist, wird nach jeder Zeile automatisch eine Zeilenschaltung ausgeführt. Es gibt Drucker, die dieses Signal gar nicht auswerten; in anderen kann die Auswertung über Konfigurations-Einstellung gesteuert werden (die übliche Voreinstellung: die automatische Zeilenschaltung ist ständig wirksam).

## /ERROR (FAULT)

ERROR (FAULT) ist aktiv Low und führt vom Gerät zum PC. Es handelt sich um die allgemeine Gerätefehleranzeige. Bei Druckern wird ERROR üblicherweise in folgenden Zuständen aktiv: (1) kein Papier, (2) nicht ausgewählt bzw. nicht "on line", (3) ein interner Fehler.

## /INIT

INIT ist aktiv Low und führt vom PC zum Gerät. Bei Aktivierung von INIT (manchmal auch als INPUT PRIME bezeichnet) wird das Gerät zurückgesetzt. Geforderte Impulsbreite:  $> 15~\mu s$ .

#### /SELECT IN

SELECT IN ist aktiv Low und führt vom PC zum Gerät. Das Gerät ist nur dann ausgewählt, wenn SELECT IN aktiv ist. Ist SELECT IN inaktiv, so darf das Gerät am Interface nicht reagieren, also die ankommenden Bytes nicht auswerten, muß aber das STROBE-BUSY-ACKNOWLEDGE-Signalspiel weiterhin mitsteuern (die Daten gehen dabei gleichsam ins Leere). Manche Geräte werten SELECT IN gar nicht aus, bei manchen ist die Auswertung konfigurierbar (die Wahlmöglichkeiten: (1) SELECT IN wird ausgewertet, (2) SELECT IN wird ignoriert und intern als ständig aktiv angesehen). Der Zweck von SELECT IN besteht darin, mehrere Geräte an einen Interface-Strang anschließen zu können (wobei das Signal von den einzelnen Geräten als Daisy-Chain-Signal durchgeleitet wird).

# 7.3.4. Funktionsbeschreibung

# 7.3.4.1. Die herkömmliche Schnittstelle (Standard Printer Port SPP)

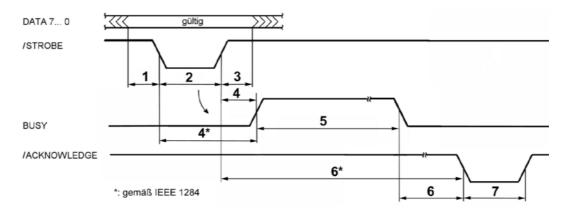

Die Abbildungen 7.9 bis 7.11 zeigen typische Signalfolgen.

Abbildung 7.9 SPP-Datenübertragung (Centronics-Handshaking). Zeitangaben in Tabelle 7.2

| Zeitkenn-<br>wert | Bedeutung                                           | Centronics, allgemein | PC        | IEEE 1284           |

|-------------------|-----------------------------------------------------|-----------------------|-----------|---------------------|

| 1                 | Daten-Vorhaltezeit                                  | ≥ 1 µs                | ≥ 0,5 µs  | $\geq$ 0,75 $\mu s$ |

| 2                 | Strobe-Impulsbreite                                 | 1500 μs               | 0,5500 μs | 0,75500μs           |

| 3                 | Daten-Haltezeit                                     | ≥ 1 µs                | ≥ 0,5 µs  | $\geq$ 0,75 $\mu s$ |

| 4                 | Verzögerung bis BUSY                                | 01,5 μs               | 0         | ≤ 500 ns*)          |

| 5                 | BUSY-Impulsdauer abhängig von den Abläufen im Gerät |                       | Gerät     |                     |

| 6                 | Verzögerung bis Acknowlege                          | 2,510 μs              | -         | 0*)                 |

| 7                 | Acknowledge-Impulsdauer                             | 2,56 μs               | ≥ 2,5 µs  | 0,5 10 μs           |

<sup>\*):</sup> andere Definition beachten (vgl. Abbildung 7.9)

Tabelle 7.2 Zeitkennwerte der Datenübertragung

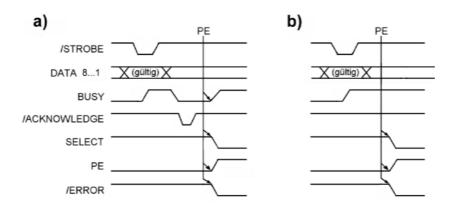

Abbildung 7.10 Signalisierung von Papierende

## Erklärung:

a) - Bedingung wurde nach Übertragung eines Bytes bzw. Abschluß eines Druckvorganges erkannt; b) - Bedingung wurde erkannt, während ein gerade übertragenes Byte noch intern verarbeitet wird.

Abbildung 7.11 Signalisierung des Übergangs in den Off-Line-Zustand

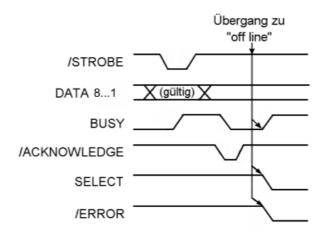

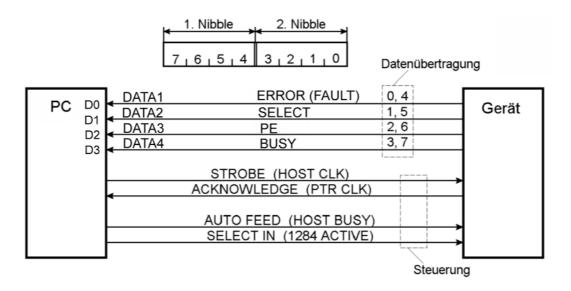

## **7.3.4.2.** Nibble Mode

In dieser Betriebsart werden 4 Zustandssignale verwendet, um Information in Form von Halbbytes (4-Bit-"Nibbles") aus dem Gerät abzuholen (Abbildung 7.12). Diese Betriebsart ist in 1284-Implementierungen obligatorisch. Sie dient zum Abfragen von Gerätekennungen (Stichwort: Plug & Play) sowie zum "Aushandeln" des eigentlichen Übertragungsverfahrens zwischen PC und Gerät.

Abbildung 7.12 Signalbelegung im Nibble Mode

## 7.3.4.3. EPP

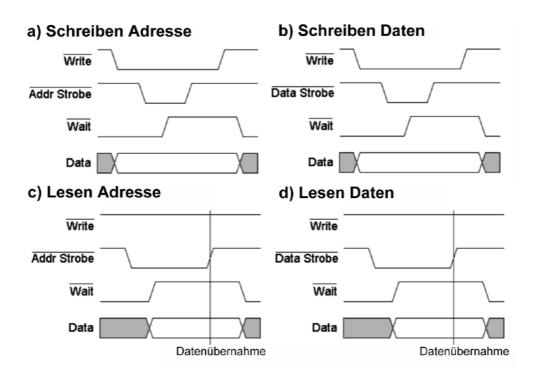

Einige Interfacesignale haben eine andere Bedeutung (Tabelle 7.3). Abbildung 7.13 gibt einen Überblick über die typischen Signalspiele.

| herkömml. Signal | EPP-Signal  | Wirkung                                                                                                |

|------------------|-------------|--------------------------------------------------------------------------------------------------------|

| STROBE           | WRITE       | Low: Schreibzugriff, High: Lesezugriff                                                                 |

| SELECT IN        | ADDR STROBE | Hostseitiges Handshakesignal für Adreßübertragung (aktiv Low)                                          |

| AUTO FEED        | DATA STROBE | Hostseitiges Handshakesignal für Datenübertragung (aktiv Low)                                          |

| BUSY             | WAIT        | Handshake-Antwortsignal des Gerätes.<br>Low: Gerät bereit/fertig, High: Gerät nicht bereit/beschäftigt |

| ACKNOWLEDGE      | INTERRUPT   | Interruptauslösung (seitens des Gerätes). Wirksam mit der Low-<br>High-Flanke                          |

| INIT             | INIT        | zeigt Rückkehr zum Compatibility-Modus an. Aktiv Low                                                   |

**Tabelle 7.3** EPP-Steuersignale. Die verbleibenden Signale PE, ERROR (FAULT) und SELECT sind gerätespezifisch nutzbar

Abbildung 7.13 Typische EPP-Signalspiele

## Zur EPP-Philosophie

Der Host (typischerweise der PC) wählt zunächst ein Register im Gerät aus und führt dann Datenzugriffe auf dieses Register aus (Schreiben oder Lesen). Ein E-A-Ablauf besteht somit aus dem Schreiben von Adressen und dem Schreiben oder Lesen von Datenbytes.

## **EPP 1.7 und EPP 1.9**

Das sind Variantenbezeichnungen: EPP 1.7 entspricht der ursprünglichen Spezifikation, EPP 1.9 dem Standard IEEE 1284. Der wesentliche Unterschied liegt darin, wie der Host auf das WAIT-Signal reagiert:

- EPP 1.9 (die saubere Lösung): der Host darf ADDRS STROBE oder DATA STROBE erst dann aktivieren, wenn WAIT = Low ist (voll verriegeltes Handshaking, wie in Abbildung 7.13 gezeigt),

- EPP 1.7: der Host wartet nicht auf WAIT = Low; er darf auch bei WAIT = High ein STROBE-Signal aktivieren. Das funktioniert nur dann richtig, wenn das Gerät darauf eingestellt ist (also enweder WAIT schnell genug wieder auf Low schaltet oder in der Lage ist, auch bei WAIT = High eine neue Datenübertragung anzunehmen). Bug oder Feature? Immerhin können auch moderne Super-IO-Schaltkreise diese Betriebsart noch emulieren...

## 7.3.4.4. ECP

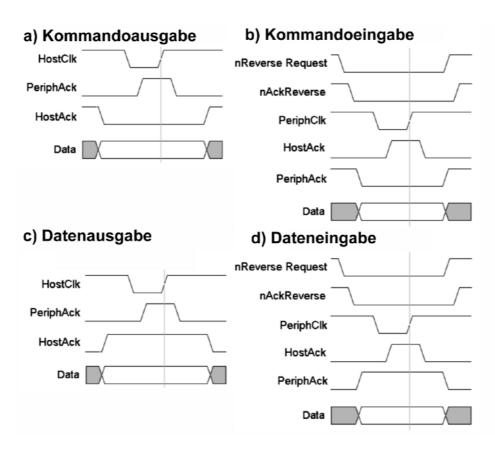

Einige Interfacesignale haben eine andere Bedeutung (Tabelle 7.4). Abbildung 7.14 gibt einen Überblick über die typischen Signalspiele.

| herkömml. Signal | EPP-Signal      | Wirkung                                                                                                                                                                                                                        |

|------------------|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STROBE           | HostClk         | Handshake-Signal vom Host. Zeigt an, daß der Host Daten auf den Bus gelegt hat. Aktiv low. Wirkt mit PeriphAck zusammen                                                                                                        |

| BUSY             | PeriphAck       | bei Ausgabe: Handshake-Signal vom Gerät. Antwort auf<br>HostAck. Zeigt an, daß das Geät die Daten übernommen hat.<br>bei Eingabe: Gerät kennzeichnet, um welche Busbelegung es sich                                            |

|                  |                 | handelt. Low: Kommandobyte, High: Datenbyte                                                                                                                                                                                    |

| AUTO FEED        | HostAck         | bei Ausgabe: Host kennzeichnet, um welche Busbelegung e sich<br>handelt Low: Kommandobyte, High: Datenbyte                                                                                                                     |

| 11010122         | 11000.100       | bei Eingabe: Handshake-Signal vom Host. Antwort auf<br>PeriphClk. Zeigt an, daß der Host die Daten übernommen hat.                                                                                                             |

| INIT             | nReverseRequest | zeigt Übertragungsrichtung an. Vom Host erregt. Low: Eingabe,<br>High: Ausgabe. Gerät darf den Bus nur dann belegen (Eingaberichtung), wenn nReverseRequest = Low und 1284 Active =<br>High                                    |

| PE               | nAckReverse     | vom Gerät erregt. Bestätigungssignal für Eingabe. Aktiv Low.<br>Host darf den Bus nur dann belegen (Ausgaberichtung), wenn<br>nAckReverse = Low                                                                                |

| ACKNOWLEDGE      | PeriphClk       | Handshake-Signal vom Gerät. Zeigt an, daß das Gerät Daten auf den Bus gelegt hat. Aktiv low. Wirkt mit HostAck zusammen                                                                                                        |

| ERROR (FAULT)    | PeriphRequest   | Anforderungssignal vom Gerät. Aktiv Low. Typischerweise zur Interruptauslösung verwendet                                                                                                                                       |

| SELECT IN        | 1284 Active     | vom Host erregt. High: Host wünscht ECP-Betrieb, Low: Rück-<br>kehr zum Compatibility-Modus                                                                                                                                    |

| SELECT           | XFlag           | vom Gerät erregt. Aktiv Low. Hiermit bestätigt das Gerät den<br>Übergang in den ECP-Betrieb. Antwortet das Gerät auf Erregung<br>von 1284 ACTIVE nicht mit XFlag = Low, so verbleibt das Inter-<br>face im Compatibility-Modus |

Tabelle 7.4 ECP-Steuersignale

Abbildung 7.14 Typische ECP-Signalspiele

## Zur ECP-Philosophie

Sie ähnelt der EPP-Philosophie. Erweiterungen:

- Unterstützung des DMA-Betriebs auf der PC-Seite,

- eingebaut FIFO-Puffer,

- Datenkompression nach dem RLE-Prinzip (RLE = Run Length Encoding).

## Kommmandobytes

Es gibt zwei Arten: RLL-Bytes und Adreßbytes. Unterscheidung: anhand des Bits 7.

- Bit 7 = Low: RLL-Byte. Die verbleibenden 7 Bits geben an, wie oft das nachfolgende Datenbyte zu wiederholen ist. Beispiel: das Zeichen "F" soll 30 mal wiederholt werden. Übertragung: (1) Kommandobyte = 29 (Binärzahl), (2) Datenbyte "F" (ASCII-Zeichen). Das Zeichen wird vom Gerät übernommen, und es werden weitere 29 gleiche Zeichen nachgeschoben (Zeichenwiederholung).

- Bit 7=High: Adreßbyte. Die verbleibenden Bits geben eine geräteinterne Adresse an (ähnlich EPP).

Wer erledigt die Datenkompression?

- a) Komprimieren = nach gleichen aufeinanderfolgenden Bytes suchen und diese durch ein RLL-Byte und ein Datenbyte ersetzen: die Software,

- b) Entkomprimieren = die ursprüngliche Anzahl an gleichen Bytes abliefern (Zeichenwiederholung): die Hardware.

## **Fast Centronics Mode (Parallel Port FIFO Mode)**

Das ist eine Sonderbetriebsart des ECP. Hierbei wird das Centronics-Handshaking des SPP (vgl. Abbildung 7.9) von der Hardware unterstützt. Um die Übertragung auszulösen, genügt es, das Byte in den FIFO-Puffer zu schreiben. Den Rest erledigt die Hardware. Zeitkennwerte (Überblick): Daten-Vorhaltezeit wenigstens 600 ns, Strobe-Impulsdauer wenigstens 600 ns, Datenhaltezeit wenigstens 450 ns, Zeit zwischen Strobe-Aktivierung und BUSY-Aktivierung höchstens 500 ns, Zeit von Deaktivierung von BUSY (Gerät ist wieder bereit) bis zum nächsten Strobe: wenigstens 680 ns.

## 7.3.4.5. EPP und ECP: Gemeinsamkeiten und Unterschiede

## Handshaking

Beide Betriebsarten nutzen ein vollständig verriegeltes (Fully Interlocked) Handshaking.

EPP (vgl. Abbildung 7.13)

Der Host beginnt jeden Übertragungszyklus mit ADDR STROBE oder DATA STROBE => Low. Daraufhin antwortet das Gerät mit WAIT => High (und zwar dann, wenn es die Busbelegung - je nach Übertragungsrichtung - entweder abgenommen oder aufgeschaltet hat). Dann schaltet der Host sein Strobe-Signal ab (beim Lesen: nachdem er die Busbelegung abgenommen hat (Datenübernahme)). Daraufhin schaltet das Gerät WAIT auf Low. Somit kann der nächste Übertragungszyklus beginnen.

ECP (vgl. Abbildung 7.14)

Es gibt ein Ausgabe- und ein Eingabehandshake:

- Ausgabe: Der Host schaltet die Daten auf den Bus und erregt HostCLK (Low). Hat das Gerät die Busbelegung abgenommen (Datenübernahme), aktiviert es PeriphAck (High). Darauf antwortet der Host mit dem Deaktivieren von HostClk (High), woraufhin das Gerät seinerseits PeriphAck deaktiviert (Low).

- Eingabe: Es ist im Grunde der gleiche Ablauf, nur mit vertauschten Rollen und anderen Signalen. Das Gerät schaltet die Daten auf den Bus und erregt PeriphClk (Low). Hat der Host die Busbelegung abgenommen (Datenübernahme), aktiviert er HostAck (High). Darauf antwortet das Gerät mit dem Deaktivieren von PeriphClk (High), woraufhin der Host seinerseits HostAck deaktiviert (Low).

Welche Handshaking-Signalspiele können wir am Interface beobachten (herkömmliche Signalbezeichner)?

- EPP: SELECT IN und BUSY oder AUTO FEED und BUSY,

- ECP: STROBE und BUSY oder ACKNOWLEDGE und AUTO FEED.

#### Hinweis:

An den Signalspielen ist meßtechnisch (Oszilloskop) ist zu erkennen, in welcher Betriebsart und mit welcher Datenrate die Schnittstelle arbeitet.

## Richtungssteuerung:

#### EPP

Der Host bestimmt die Übertragungsrichtung. Signalisierung über Signal WRITE.

#### ECP

Fachbegriffe: Ausgaberichtung = Forward Direction, Eingaberichtung = Reverse Direction. Zur Richtungssteuerung gibt es ein besonderes Handshaking:

- Umschalten auf Eingaberichtung: der Host gibt den Bus frei und aktiviert nReverseRequest.Ist das Gerät in der Lage, den Bus zu belegen, antwortet es mit nAckReverse.

- Umschalten auf Augaberichtung: der Host deaktiviert nReverseRequest. Daraufhin gibt das Gerät den Bus frei und deaktiviert nAckReverse. Ist nAckRevese inaktiv, darf der Host den Bus wieder belegen.

## Unterscheidung zwischen Daten- und Adreß-oder Kommandoübetragung:

## EPP

Je nachdem, welche Übertragung er wünscht, wählt der Host das betreffende Handshake-Signal (ADDR STROBE oder DATA STROBE).

#### ECP

Die liefernde Einrichtung zeigt an, worum es sich jeweils handelt:

- Ausgabe: Anzeige vom Host über HostAck,

- Eingabe: Anzeige vom Gerät über PeriphAck.

(Jeweils: Low = Kommando-, High = Datenbyte. Die Abläufe in Abbildung 7.14 a, c und b, d unterscheiden sich nur durch die Belegung von HostAck bzw. PeriphAck.)

# 7.4. Parallele Schnittstellen im PC

## Die herkömmliche Parallelschnittstelle

Eine Parallelschnittstelle wird im PC softwareseitig über drei aufeinanderfolgende E-A-Adressen angesprochen. Dabei muß die Software das Übertragen der einzelnen Bytes steuern und Rückmeldungen des Gerätes abfragen. Die Datenübertragung selbst kann wahlweise nach dem Abfrageprinzip oder nach dem Interruptprinzip gesteuert werden.

#### Wieviele Schnittstellen?

Das hängt von der Ebene ab, auf der die Software die Interfaces steuern soll. Von der Anwendung aus (oder über spezielle Gerätetreiber) kann man an sich beliebig viele Schnittstellen vorsehen, sofern diese mittels Abfragesteuerung betrieben werden.

Allgemein üblich ist aber die Steuerung über das BIOS, das bis zu drei derartige Schnittstellen unterstützt. Davon können zwei im Interruptverfahren gesteuert werden. Tabelle 7.5 zeigt die Belegung der E-A-Adressen.

| parallele Schnittstelle | Bereich der E-A-Adressen | Interrupt |

|-------------------------|--------------------------|-----------|

| 1.                      | 3BC3BEH                  | 7         |

| 2.                      | 37837AH                  | 7         |

| 3.                      | 27827AH                  | 5         |

Tabelle 7.5 Die E-A-Adressierung der parallelen Schnittstellen

#### **BIOS und DOS**

Die BIOS-Funktionen zur Schnittstellensteuerung erwarten keine E-A-Adressen, sondern laufende Nummern (von 0 bis 2); in DOS werden die Schnittstellen durch die (reservierten) Port-Bezeichner LPT1 (bzw. gleichbedeutend PRN), LPT2, LPT3 angesprochen. Die Zuordnung zwischen E-A-Adresse und Schnittstellennummer wird nach dem Rücksetzen getroffen, und zwar im Rahmen des Anfangstests POST. Dieser prüft die drei in Frage kommenden Adreßbereiche und ordnet diese, falls er dort eine Schnittstellen-Hardware vorfindet, den laufenden Nummern des BIOS in aufsteigender Reihenfolge zu. Dieser Reihenfolge entsprechen dann die DOS-Bezeichnungen LPT1...LPT3. Die Reihenfolge der Abfrage: (1) ab 378H, (2) ab 378H, (3) ab 278H. Die erste in dieser Prüfreihenfolge vorgefundene Schnittstelle wird für DOS zu LPT1, die zweite zu LPT2 usw. Die Zuordnung ist aus dem RAM ersichtlich (Tabelle 7.6).

#### Hinweis:

Die Schnittstelle auf Adresse 3BCH ist in älteren PCs auf der MDA- bzw. Herkules-Videokarte vorgesehen. In modernen PCs liegt LPT1 üblicherweise auf E-A-Adresse 378H (und folgenden).

| Adresse (Segment:<br>Offset in Hex) | Inhalt                | Adresse (Segment:<br>Offset in Hex) | Inhalt                       |

|-------------------------------------|-----------------------|-------------------------------------|------------------------------|

| 0040:0008                           | 1. E-A-Adresse LPT1   | 0040:0078                           | Timeout-Zählerendwert LPT1   |

| 0040:000A                           | 1. E-A-Adresse LPT2   | 0040:0079                           | Timeout-Zählerendwert LPT2   |

| 0040:000C                           | 1. E-A-Adresse LPT3   | 0040:007A                           | Timeout-Zählerendwert LPT3   |

| 0040:000E                           | (1. E-A-Adresse LPT4) | 0040:007B                           | (Timeout-Zählerendwert LPT4) |

Tabelle 7.6 Parallelschnittstellen: Angaben im RAM

## **Zeitkontrolle (Timeout)**

Das BIOS realisiert eine einfache Form der Zeitüberwachung für die unterstützten Parallelschnittstellen: immer dann, wenn ein neues Zeichen übertragen werden soll, das Gerät aber noch nicht dazu bereit ist, wird ein Zählwert vermindert. Der Zählwert Null veranlaßt eine Fehlermeldung. Beachten Sie, daß es sich hierbei nicht um eine Zeitüberwachung, sondern um eine Durchlauf- bzw. Schleifenzählung handelt. Ein schneller Prozessor läßt so - bei gegebenem Anfangswert - dem Gerät weniger Zeit zum Reagieren als ein langsamer. Im BIOS wird dies dadurch ausgeglichen, daß der vorgegebene Zählwert mit einem gewissen festen Faktor multipliziert wird (der im jeweiligen BIOS gemäß dem Prozessortyp eingestellt ist). Manche Anwendungsprogramme beeinflussen die Zähler-Endwerte (es handelt sich um jederzeit zugängliche Bytes im RAM; vgl. Tabelle 8.2), um ihrerseits eine Zeitkontrolle auszuüben.

## Eingabeoperationen über die Parallelschnittstelle

Die einwärtsführenden Schnittstellensignale lassen sich softwareseitig lesen und eignen sich somit dazu, Daten zum PC zu übertragen.

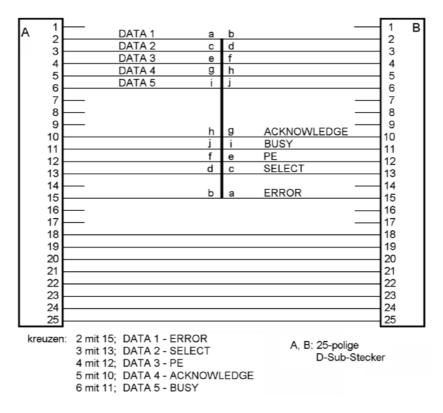

## Paralleles Nullmodem-Kabel (PC-Direktverbindung)

Manche Datenaustausch- und Fernbedienungsprogramme (Interlink (DOS), die PC-Direktverbindung (Windows), Laplink, PCAnywhere usw.) nutzen ein spezielles Kabel, um zwei PCs über Parallelschnittstellen miteinander zu verbinden (Abbildung 7.15). Darüber lassen sich jeweils 4 Bits parallel übertragen (über die fünfte Verbindung wird ein softwaregesteuertes Handshaking organisiert).

Abbildung 7.15 Paralleles Nullmodemkabel (PC-Direktverbindung)

## Die Register der parallelen Schnittstelle

Abbildung 7.16 zeigt die Registerbelegung einer Parallelschnittstelle, die zum PS/2 kompatibel ist und die in beiden Richtungen (bidirektional) genutzt werden kann.

| Bitposition           | 7      | 6                 | 5      | 4      | 3            | 2      | 1            | 0          | LPT1 | LPT 2 | LPT 3 |

|-----------------------|--------|-------------------|--------|--------|--------------|--------|--------------|------------|------|-------|-------|

| Daten-<br>register    | DATA 8 | DATA 7            | DATA 6 | DATA 5 | DATA 4       | DATA 3 | DATA 2       | DATA 1     | звсн | 378H  | 278H  |

| Zustands-<br>register | /BUSY  | /ACKNOW-<br>LEDGE | PE     | SELECT | /ERROR       | /PRINT | (fe<br>1     | st)<br>  1 | 3BDH | 379H  | 279H  |

| Steuer-<br>register   | 0 re   | es.<br>0          | DIR    | INT2EN | SELECT<br>IN | /INIT  | AUTO<br>FEED | STROBE     | звен | 37AH  | 27AH  |

Abbildung 7.16 Registerbelegung

## Richtungsumsteuerung

Zur Richtungsumsteuerung ist das Bit DIR im Steuerregister vorgesehen:

- DIR = 0: Auswärtsbetrieb. Die Datenleitungen werden vom PC aus erregt.

- DIR = 1: Einwärtsbetrieb. Die Datenleitungen werden inaktiv geschaltet und können so von außen belegt werden.

In Schnittstellenhardware, die nicht für den Byte-Modus (PS/2-Betrieb) vorgesehen ist, liegt das DIR-Bit fest auf 0 und kann auch nicht umgeschaltet werden.

## Betriebsartensteuerung

Der erweiterte (PS/2-) Modus ist typischerweise abschaltbar. Im herkömmlichen (Compatibility-) Modus ist das Bit DIR (Steuerregister) wirkungslos (statt dessen: Festwert 0), und das Bit /PRINT (Zustandsregister) schaltet nicht (statt dessen: Festwert 1). *Hinweis:* In der Festwertbelegung kann es gelegentlich Abweichungen geben.

#### **Datenregister**

Das Datenregister gibt die Belegungen der 8 Datenleitungen wieder. Es kann geschrieben und gelesen werden. Die Wirkungen der Zugriffe in den verschiedenen Betriebsarten:

- DIR = 0 (Auswärtsbetrieb): Schreibzugriffe wirken sich unmittelbar auf die Datenleitungen aus, Lesezugriffe geben den Registerinhalt zurück,

- DIR = 1 (Einwärtsbetrieb): Schreibzugriffe ändern nur den Registerinhalt, Lesezugriffe geben die Belegung der Datenleitungen zurück.

## Zustandsregister

Dieses Register kann nur gelesen werden. Die Lesezugriffe geben die Belegung der entsprechenden Interfaceleitungen zurück. Ist kein Gerät angeschlossen, so enthält das Register nach dem Rücksetzen die Belegung 7FH. Die einzelnen Bits bedeuten:

- /BUSY: die invertierte Belegung der BUSY-Leitung (ist das Bit auf 0 gesetzt, ist die BUSY-Leitung aktiv (High)),

- /ACKNOWLEDGE: die Belegung der /ACKNOWLEDGE-Leitung,

- PE: die Belegung der PE-Leitung (Papierende),

- SELECT: die Belegung der SELECT-Leitung,

- /ERROR: die Belegung der /ERROR-Leitung,

- /PRINT (PRINTER INTERRUPT): das Gerät hat die vorhergehende Datenübertragung mit einem ACKNOWLEDGE-Impuls bestätigt. Nach jedem Lesen des Zustandsregisters wird PRINT auf 1 gesetzt. /PRINT wird durch eine Low-High-Flanke auf der Leitung /ACKNOWLEDGE aktiviert (auf 0 gesetzt). Beim Rücksetzen wird das Bit auf 1 gesetzt. Das Bit wirkt nur im Byte-Modus (PS/2-Betrieb). Ansonsten ist es fest mit 1 belegt.

#### Hinweis:

/PRINT wird von einer Fangschaltung für ACKNOWLEDGE-Impulse angesteuert. Der Zweck: die Acknowledge-Erregung so zu fixieren, daß sie garantiert mittels Software abgefragt werden kann. (Die Dauer von ACKNOWLEDGE wird ausschließlich vom Gerät bestimmt; es gibt kein entsprechendes Handshaking-Protokoll. Die Gefahr: bei direkter Abfrage der Signalbelegung könnte es vorkommen, daß zu schmale Impulse nicht erfaßt werden.)

#### Steuerregister

Auf dieses Register sind Lese- und Schreibzugriffe möglich. Schreibzugriffe wirken sich unmittelbar auf die Interfaceleitungen aus, Lesezugriffe geben den Registerinhalt zurück. Die Bedeutung der einzelnen Bits:

- STROBE: über das Bit wird die Leitung /STROBE invertiert angesteuert (durch Setzen auf 1 wird /STROBE aktiv (Low)).

- AUTO FEED: über das Bit wird die Leitung /AUTO FEED invertiert angesteuert (durch Setzen auf 1 wird /AUTO FEED aktiv (Low)).

- /INIT: über das Bit wird die Leitung /INIT direkt angesteuert.

- SELECT IN: über das Bit wird die Leitung /SELECT IN invertiert angesteuert (durch Setzen auf 1 wird /SELECT IN aktiv (Low)).

- INT2EN: Ist das Bit gesetzt, veranlassen Impulse auf der Leitung /ACKNOWLEDGE, daß der entsprechende Interrupt ausgelöst wird. Ist das Bit gelöscht, wird kein Interrupt ausgelöst. Die betreffende Interruptleitung des Steuerschaltkreises wird dann hochohmig, so daß eine andere Einrichtung diese Interruptleitung erregen kann.

- DIR: Richtungssteuerung (nur im Byte-Modus (PS/2-Betrieb)): DIR = 0 Auswärtsbetrieb, DIR = 1 Einwärtsbetrieb.

## Das Steuerregister nach dem Rücksetzen

Es ist vollständig mit Nullen geladen (damit wird die /INIT-Leitung aktiv (Low), alle anderen vom Register gesteuerten Leitungen werden inaktiv (High).

## **Der EPP-Registersatz**

Er umfaßt 8 Register (Abbildung 7.17). Die ersten 3 Register entsprechen denen der herkömlichen Schnittstelle.

| Adreß-Offset*) | Register            |

|----------------|---------------------|

| 0              | Datenregister (SPP) |

| 1              | Zustandsregister    |

| 2              | Steuerregister      |

| 3              | EPP-Adreßport       |

| 4              | EPP-Datenport 0     |

| 5              | EPP-Datenport 1     |

| 6              | EPP-Datenport 2     |

| 7              | EPP-Datenport 3     |

<sup>\*):</sup> bezogen auf die erste E-A-Adresse der Schnittstelle

Abbildung 7.17 Der EPP-Registersatz im Überblick

## **Der ECP-Registersatz**

Er umfaßt 6 Register (Abbildung 7.18). Die Nutzung der Datenregister (Offsets 0 und 400H) hängt von der jeweils gewählten Betriebsart ab. In einigen Betriebsarten handelt es sich nicht um einfache Register, sondern um FIFO-Puffer (typische Tiefe: 16 Bytes). Die etwas merkwürdig anmutende Anordnung im Adreßraum (Offset 400H uw.) hängt mit der Entwicklungsgeschichte zusammen. (Es war erforderlich, auf die herkömmliche Adreßraumaufteilung Rücksicht zu nehmen (Konfliktvemeidung). Deshalb hat man höhere, bisher im PC nicht genutzte Adressen verwendet.)

| Adreß-Offset*) | Register |

|----------------|----------|

|----------------|----------|

| 0    | Datenregister (SPP)<br>Adreß-FIFO (EPP)                                                                    |

|------|------------------------------------------------------------------------------------------------------------|

| 1    | Zustandsregister                                                                                           |

| 2    | Steuerregister                                                                                             |

| 400H | Daten-FIFO (Fast Centronics Mode)<br>Daten-FIFO (ECP)<br>Test-FIFO (Testmodus)<br>Konfigurationsregister A |

| 401H | Konfigurationsregister B                                                                                   |

| 402H | erweitertes Steuerregister                                                                                 |

<sup>\*):</sup> bezogen auf die erste E-A-Adresse der Schnittstelle

Abbildung 7.18 Der ECP-Registersatz im Überblick

## Betriebsartenumschaltung

Die jeweilige Betriebsart der Schnittstelle wird in besonderen Konfigurationsregistern des Super-IO-Schaltkreises eingestellt. Die übliche Form der Einstellung im PC: vom BIOS während des POST (Betriebsartenwahl im Setup). Von Hand ist es recht mühselig...

## Praxistips:

- 1. Zum Fehlersuchen genügt die SPP-Schnittstelle meist vollauf (Kurzschlußprüfung, meßtechnische Prüfung der Signalintegrität (Oszilloskop), probeweises Ansprechen von Druckern usw.).

- 2. Hat sich eine Schnittstelle im SPP-Modus als funktionsfähig erwiesen, kann man die Fehlersuche im Normalbetrieb fortsetzen (Gerät anschließen, ggf. Betriebsart im Setup einstellen, System hochfahren und sehen, ob es funktioniert). Fehlerzuordnung (Super IO (Motherboard) oder Gerät) ggf. durch Austauschprüfung. Nach entsprechend scharfer Testsoftware umsehen (gibt es gelegentlich zu den Geräten). EPP- oder ECP-Programmierung "zu Fuß" ist typischerweise zu kompliziert (zumal man auch noch das Programmierhandbuch des angeschlossenen Gerätes braucht).

- 3. Kostenlose Informationen zu den Betriebsarten, Signalfolgen und Registern: aus den Datenbüchern der Super-IO-Schaltkreise(Internet).