|

|

|

|

The focus:

Turning a processor temporarily into a microprogrammed control unit.

The design rationale

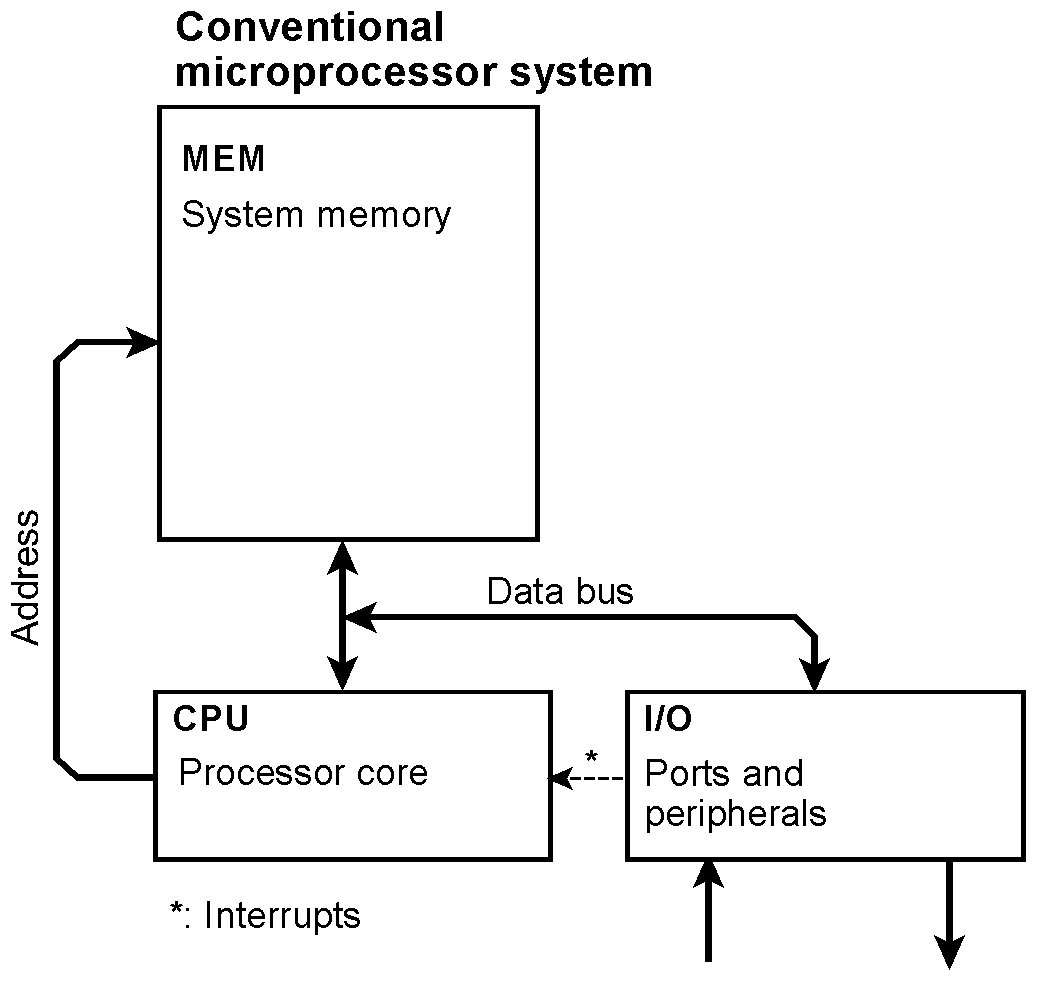

The key point is programmability down to the register transfer level (RTL). Microprogramming is a viable design idea. A microprogrammed control unit could be a much more efficient conductor of an ensemble of functional units than a conventional RISC core. This is because the latter can only affect the functional units by I/O, while a microprogram control unit could energize all control signals at once and query all condition signals immediately.

The principal obstacle

It is the vast amount of software today's users expect to run. Writing small microprograms is not that difficult at all. Creating integrated development environments (IDEs) to write big microprograms is a demanding but not insoluble task. Once it has been solved successfully, however, the complete system and application environments would have to be recompiled. So it's no wonder that developers prefer widespread processor architectures and try to solve performance problems by adding more hardware, be it more processor cores, be it dedicated accelerators.

The principal design idea:

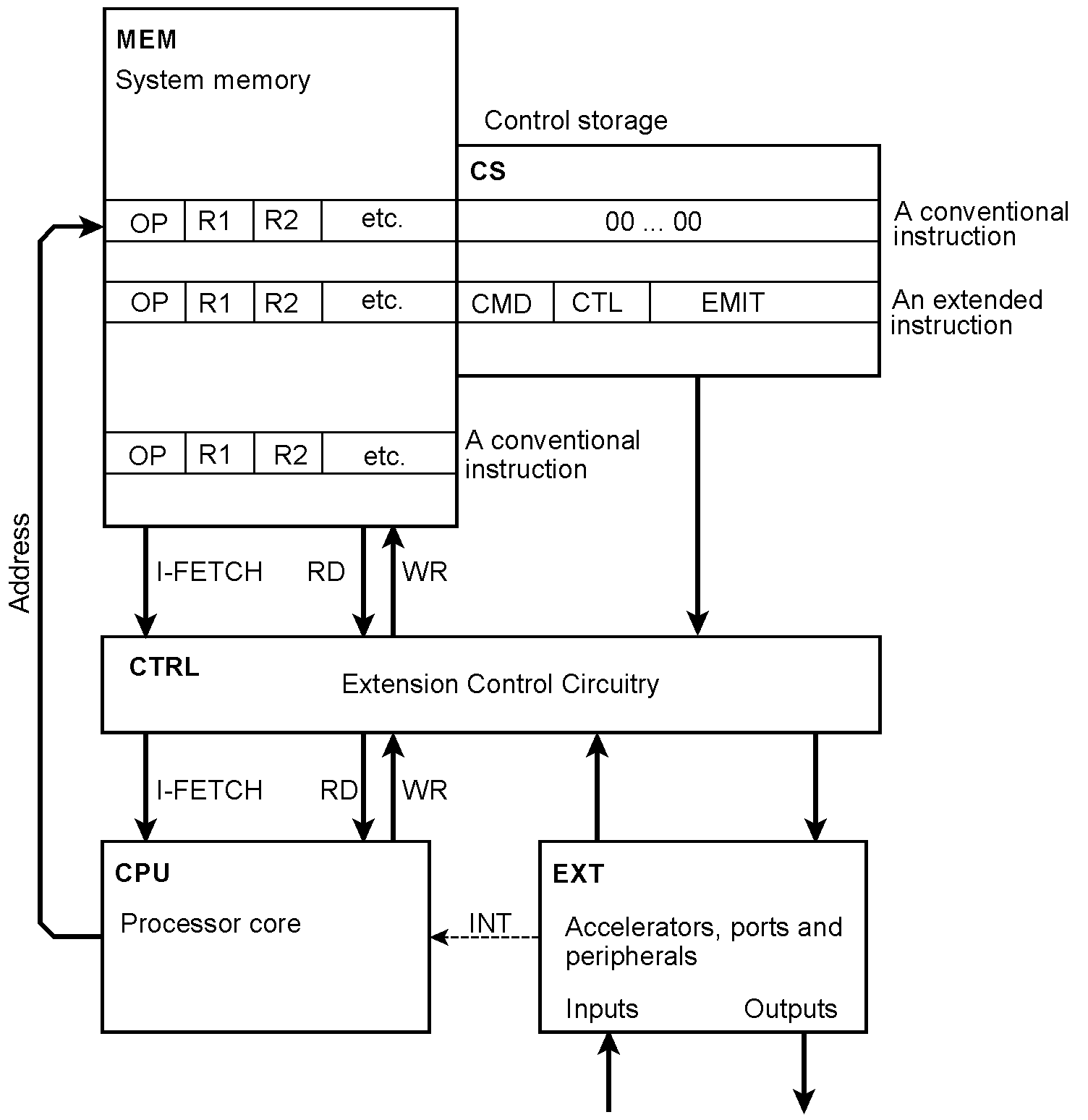

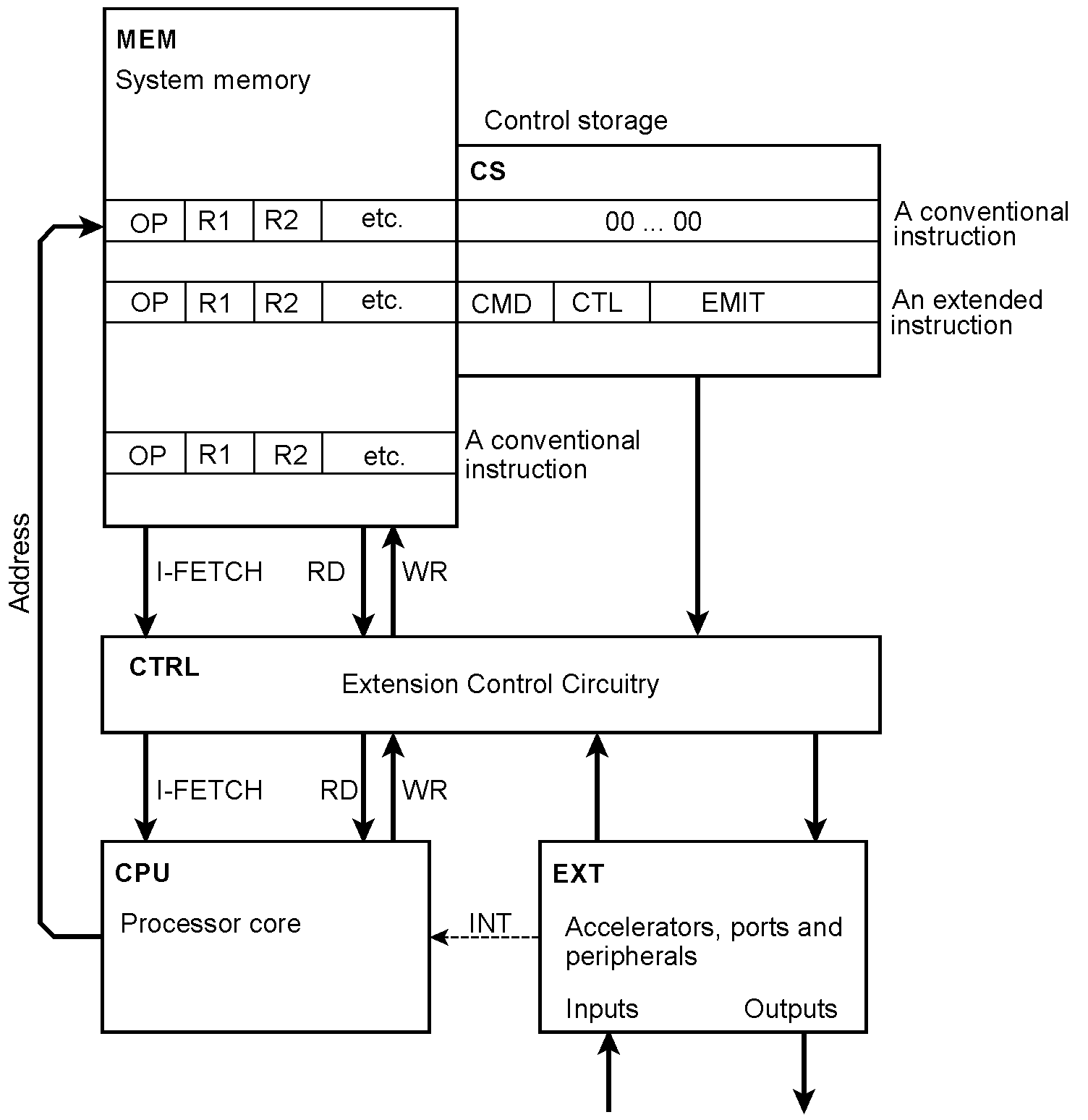

We stay with a processor core of a well-proven industry-standard architecture. Most of the software will run fast enough. Only some code snippets require to be accelerated, for example, innermost loops of complex algorithms and I/O routines interacting closely with outside circuitry. To speed up such programs, we extend the instructions outside the processor core. Inside, it will remain as it is. The instructions are extended by additional bits stored in a control storage. It is addressed in parallel to the system memory. During instruction fetch, the instruction is read out of the system memory, and the additional bits (the extension) are read out of the control storage. Outside the processor core, those extended instructions act like microinstructions.Software that does not use the extensions will run unaffected.

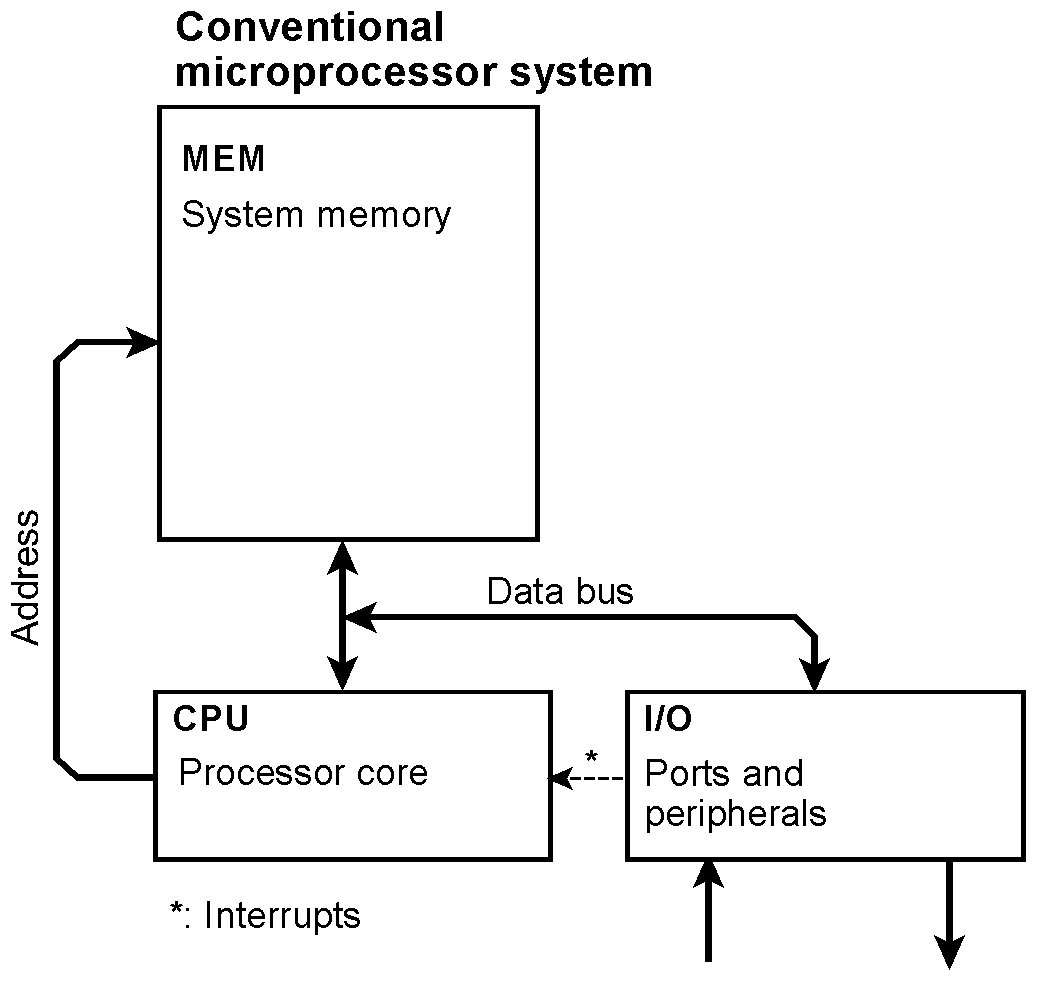

A conventional processor core can control and query I/O circuitry, accelerators, and the like merely via I/O instructions.

A control storage delivers additional bits when instructions are fetched. Outside the processor core, such extended instructions behave like microinstructions.

Some more details. If the addressed word in the contrSome more details. If the addressed word in the control storage contains only zeros (zero extension), the instruction has no additional effect. Thus extended and conventional instructions can be intermixed freely.

Examples of extended functions:

- Emit data.

- Energize additional circuitry, like accelerator units or application-specific I/O.

- Branch on I/O bits.

- Execute the instruction depending on certain conditions (predication).

- Execute an alternate instruction.

- Disable interrupts temporarily.

- Employ the address sent by the processor as additional data to be emitted.

- Facilitate compare stop functions (with an unlimited number of hardware breakpoints).

More References Project history

|

|

|

|

September 26, 2022

Download the Internet Addendum to the CC article

Download a short synopsis concerning the theory of operation

Download chapter 7. Yes, it is in German. However, an Internet translator should do it.

Download three short papers written in the Eighties (under frugal conditions with modest equipment). The examples refer to the Z80 microprocessor.

Memory Combines Parity Checking with Program Tracing Support

Additional Control Memory Improves Performance of Low-Cost Microprocessors

Hardware Support for Testability, Debuging , and Better Performance

Download a synopsis of (more or less) tricky circuitry to be attached to microprocessors, written (of course in German) in the Seventies and Eighties

Download an excerpt from this book (in German, despite the title):

|